国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

101 - 110 / 247

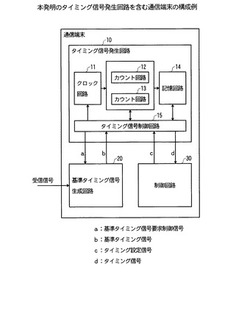

タイミング信号発生回路

【課題】 種々の時間間隔のタイミング信号を低コストで正確に発生させる。

【解決手段】 クロック回路と、クロック信号を入力するカウント回路と、外部から入力する基準タイミング信号を取得し、少なくとも2以上の基準タイミング信号を含む所定の2時点間のカウント回路のカウント値の増分と、該2時点間の時間とを対応させて記録する記憶回路と、カウント回路が所定の2時点間に対応するカウント値だけ増分した時点を中心とする所定の期間に基準タイミング信号を取得し、基準タイミング信号を受信した時点のカウント回路のカウント値を所定の2時点間に対応するカウント値として記録し、所定の2時点間の時間を周期とするタイミング信号をカウント回路のカウント値の増分を契機として発生させ、さらに基準タイミング信号を取得し、基準タイミング信号を取得した時点からカウント値の増分を計数し直す制御手段とを備える。

(もっと読む)

位相制御装置、位相制御プリント板、制御方法

【課題】出力信号の位相を微小に制御することを課題とする。

【解決手段】第1の遅延ラインでは、入力信号の入力を受け付けると、信号の位相に対して遅延量を加える遅延器各々によって当該入力信号の位相に対して遅延量を加えるとともに当該遅延器ごとの遅延信号を出力し、DLL回路では、第2の遅延ラインが、外部にて周波数の異なる信号に切り替えることが可能である外部信号の入力を受け付けると、遅延器各々によって当該外部信号の位相に対して遅延量を加え、第2の遅延ラインの複数の遅延器すべてによって遅延された遅延信号と、当該第2の遅延ラインにて遅延量が加えられていない外部信号との位相差を比較し、位相比較器によって比較される遅延信号を外部信号に同期させる電圧であって、当該位相比較器によって出力された位相差から生成された制御電圧を、第1の遅延ラインおよび第2の遅延ラインの複数の遅延器各々に入力する。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

クロックデータリカバリ回路

【課題】本発明はクロックデータリカバリ回路に関し,受信データに同期したクロックを生成し,データのタイミングを調整し,ジッタ特性を改善することを目的とする。

【解決手段】入力データ変化を検出し,パルス生成するデータ変化パルス生成手段とこの信号を平滑化する第1ループフィルタと第2クロック信号の間の位相差信号を生成する位相差信号生成手段と,この信号を平滑化する第2ループフィルタと制御信号生成手段の信号を平滑化する第3ループフィルタと,第1及び第2ループフィルタの信号から制御信号を生成する制御信号生成手段と,位相差信号生成手段の信号に基づき第1クロック信号周期に応じた時間幅の第3クロック信号を供給する高周波ジッタ吸収用クロック生成手段と,第3ループフィルタからの信号の電圧レベルに応じて第1クロック周波数を可変供給する電圧制御発振手段で入力データに同期した第1クロック信号を再生するよう構成する。

(もっと読む)

バーニア遅延回路、それを用いた時間デジタル変換器および試験装置

【課題】高精度にキャリブレーションが可能なバーニア遅延回路を提供する。

【解決手段】リングオシレータ10は、入力されたバイアス信号SbiasGに応じた周波数で発振する。バイアス信号調節部12は、リングオシレータ10の発振周波数が、所定の基準周波数と一致するように、帰還によりリングオシレータ10に対するバイアス信号SbiasGを生成する。個別バイアス回路14は、N個の第2可変遅延素子D21〜D2Nごとに設けられた複数のバイアス回路BIAS1〜BIASNを備える。各バイアス回路BIAS1〜BIASNは、バイアス信号Sbias2A1〜Sbias2ANを個別に調節可能に構成される。

(もっと読む)

クロック発生機能付き装置、基準周波数等設定方法、および基準周波数等調整方法

【課題】クロックに関する設定を簡単に行う。

【解決手段】VCXOと、基準周波数とこの基準周波数のクロックをVCXOに発生させる電圧のレベルである基準レベルとを記憶するメモリと、必要な周波数のクロックを、メモリに記憶されている基準周波数および基準レベルを基準に求められる電圧をVCXOに与えて発生させるD/Aコンバータ制御部およびD/Aコンバータと、を有する装置において、下記の処理を行う。試験時レベルを適宜変化させながら、各試験時レベルに応じた電圧をVCXOに与えて試験用クロックを発生させる。試験用クロックを周波数カウンタに出力する。試験用クロックの周波数と目標周波数との差が所定の範囲内であることが周波数カウンタによって確認できたら、メモリに、この試験用クロックがVCXOによって発生された際の試験時レベルを基準レベルとして記憶させ、この試験用クロックの周波数を基準周波数として記憶させる。

(もっと読む)

CDR回路

【課題】再生クロックのジッタを低減する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスにより発振位相が制御されるクロックを生成するゲーテッドVCO3と、フィードバック入力端子にゲーテッドVCO3の出力クロックが入力され、ゲーテッドVCO3の出力クロックと同じ周波数の再生クロックを生成するVCO4と、入力データを遅延させる遅延回路5と、遅延回路5を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路で低消費電力で帯域制限された正確な短パルスの発生回路を具現。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点からから所定量の時間差で位相が順次変化するn個の信号(nは2以上の整数)を発生するタイミング発生回路10と、起動信号から発生しようとするパルスの継続時間に相当するパルス幅のパルス幅信号を発生するパルス幅信号発生回路30と、パルス幅信号の帯域を制限するフィルタ回路142,143と、所定の電位を供給する第1の電源147及び第2の電源146と、フィルタ回路142,143の出力値によってそのインピーダンス値が制御される可変インピーダンス回路144,145と、n個の信号の少なくとも一部の信号の論理関数値によって出力端子と第1の電源または第2の電源とを可変インピーダンス回路を介して交互に切り替えて接続する。

(もっと読む)

CDR回路

【課題】製造のばらつきや環境変化あるいは入力データのパルス幅歪に対して強い耐性を持つCDR回路を提供する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、周波数制御信号に応じて発振周波数が制御されかつゲーティング回路2の出力パルスにより発振位相が制御される再生クロックを生成するゲーテッドVCO3と、入力データを遅延させる遅延回路4と、遅延回路4を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。遅延回路4は、ゲーティング回路2と同じ構成の遅延回路であるレプリカ回路40と、ゲーテッドVCO3と同じ構成の遅延回路であるレプリカ回路41とから構成される。

(もっと読む)

101 - 110 / 247

[ Back to top ]