国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

71 - 80 / 247

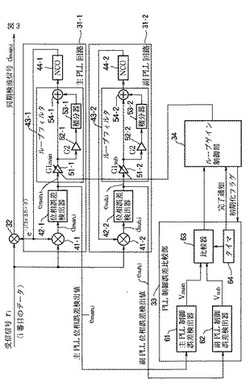

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

周波数同期装置、受信機および周波数同期方法

【課題】インパルス状の外乱が生じる環境でも、精度の良い周波数同期を確立することができる周波数同期装置を得ること。

【解決手段】再生周波数を受信信号に同期させる周波数同期制御を行う周波数同期装置であって、受信信号に基づいて周波数偏差を求める周波数偏差検出部2と、周波数偏差の時間変化量を算出する差分部3と、時間変化量に基づいて、前記周波数偏差を周波数制御値として用いるか否かを示す制御値選択信号を生成する観測部6と、制御値選択信号が周波数偏差を周波数制御値として用いないことを示す値であった場合には、過去の周波数制御値に基づいてその時点での周波数制御値の推定値である推定制御値を求め、求めた推定制御値を周波数制御値として選択するホールド部7と、を備える。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

衛星ナビゲーションシステムのためのマスタークロック生成装置

【課題】低廉な製作コスト及び部品コストで製造することができ、更に、マスタータイミング基準信号をより高精度で生成することのできる衛星ナビゲーションシステムのためのマスタークロック生成装置の提供。

【解決手段】複数の周波数信号入力部の各々に、原子時計信号から成る第1参照周波数信号と、原子時計信号から成る第2参照周波数信号との、いずれか一方を供給する。複数の周波数コンバータ(110、115、120、125)は、互いに同一周波数の中間周波数信号を出力する。スイッチングマトリクス130は、前記中間周波数信号のうちの1つを主クロックとして選択して送出すると共に、別の1つを副クロックとして選択して送出する。周波数信号生成器150は、前記主クロックから基準周波数信号を生成し、複数の周波数信号出力部へ送出する。位相メーター170は、前記主クロックと前記副クロックとの間の位相差を測定し、異常挙動を検出する。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

バッファーガス混合比設定方法、原子発振器の周波数調整方法、及び原子発振器

【課題】ガスセルの温度を一義的に定めることで原子発振器の中心周波数を微小に調整す

ることができる原子発振器の周波数調整方法を提供する。

【解決手段】半導体レーザにより構成される光源1と、所定の混合比のバッファーガス及

びアルカリ金属原子を封入したガスセル2と、ガスセル2を所定の温度に加熱するヒータ

ー8と、所望の周波数になるようにヒーター8の温度を設定する温度設定回路10と、ヒ

ーター8の温度を検知する温度センサー7と、ヒーター8を温度設定回路10により設定

された温度に保持する温度制御回路9と、ガスセル2の透過光を検出する光検出回路3と

、光検出回路3により検出されたEIT信号に基づいて同期制御を行なう制御回路4と、

制御回路4からの制御信号に従い、出力周波数が制御される電圧制御水晶発振器5と、電

圧制御水晶発振器6の出力信号を逓倍してマイクロ波を発生するマイクロ波発生回路6と

、を備えて構成される。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、パルスカウンタ12、充電回路13、リセット回路14、調整回路15及びタイミング制御部を備えている。タイミング制御部から供給されたカウント開始信号に基づいてパルスカウンタ12は、発振回路11から出力される周波数f0のパルス信号をカウントし、この間、出力信号S1を充電回路13に供給する。充電回路13は、出力信号S1が供給されている間、定電流減PS1とコンデンサC1とを接続し、接続ノードND1の電圧V1を上昇させる。調整回路15は、出力信号S1の出力が終了した場合の電圧V1が、高電位基準電圧VHより高い場合には、周波数f0を高くする調整値を発振回路11に供給し、低電位基準電圧VLより低い場合には、周波数f0を低くする調整値を発振回路11に供給する。

(もっと読む)

71 - 80 / 247

[ Back to top ]