国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

81 - 90 / 247

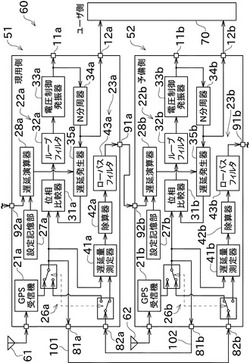

基準周波数発生システム及び基準周波数発生装置

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のGPS受信機21aからケーブル101を介して出力された1PPS信号がPLL回路22bに供給される。予備側に入力された1PPS信号は、ケーブル101と遅延量が等しいケーブル102を介して現用側に戻される。現用側の基準周波数発生装置51は、自機のGPS受信機21aからの1PPS信号と、予備側に出力して戻された1PPS信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、パルスカウンタ12、充電回路13、リセット回路14、調整回路15及びタイミング制御部を備えている。タイミング制御部から供給されたカウント開始信号に基づいてパルスカウンタ12は、発振回路11から出力される周波数f0のパルス信号をカウントし、この間、出力信号S1を充電回路13に供給する。充電回路13は、出力信号S1が供給されている間、定電流減PS1とコンデンサC1とを接続し、接続ノードND1の電圧V1を上昇させる。調整回路15は、出力信号S1の出力が終了した場合の電圧V1が、高電位基準電圧VHより高い場合には、周波数f0を高くする調整値を発振回路11に供給し、低電位基準電圧VLより低い場合には、周波数f0を低くする調整値を発振回路11に供給する。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

基準周波数発生装置

【課題】ユーザ側装置で立上りタイミングが一致した2つの信号を容易に得られる基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、ユーザ側装置へ10MHz及び1Hzの信号をそれぞれ出力する2つの出力端子と、ユーザ側装置から戻された上記信号をそれぞれ入力する2つの入力端子と、を備える。基準周波数発生装置を初めてユーザ側装置に接続したときは、2つの出力端子から出力される波形は何れも、その立上りタイミングがUTCの1秒に正確に同期している。この基準状態で、出力する1Hzの波形と、ユーザ側装置から戻された1Hzの波形との間で、立上りタイミングの差が測定される。また、ユーザ側装置から戻された1Hzの波形と、同様に戻された10MHzの波形との間で、立上りタイミングの差が測定される。CPUは、得られた時間差に基づき、10MHz及び1Hzの出力信号波形の位相を所定の関係に従って調整する。

(もっと読む)

半導体装置

【課題】従来のデューティ検出回路では、キャパシタに対するプリチャージ後の充放電動作が、通常のデューティ検出動作中の充放電動作とは異なるものとなり、正確なデューティ検出ができなかった。

【解決手段】内部クロック信号CLKがハイレベルを取る期間とロウレベルを取る期間との比(デューティ比)を積算し、電気的に記憶する記憶部(キャパシタC1,C2)と、記憶部(キャパシタC1,C2)における積算動作(デューティ検出動作)を制御する積算動作制御回路42と、一端が積算動作制御回路42と接続され、他端が電源線(VDD,GND)に接続された定電流回路(バイアストランジスタBTr1,BTr2)と、積算結果を初期化するプリチャージ回路43とを備え、プリチャージ回路43による初期化の実施中に電流回路(バイアストランジスタBTr1,BTr2)に電流を流すようにする。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

基準信号発振装置及び基準信号発振方法

【課題】基準信号の周波数を容易かつすばやく校正し、無線基地局の安定動作を実現すること。

【解決手段】GPSユニット14と、基準信号を発振し、電圧を印加することで前記基準信号の周波数が可変する発振源22と、予め定められた測定時間における基準信号のパルス数を測定し、予め定められた基準パルス数からの測定したパルス数の誤差を示す周波数偏差tfを測定する制御ユニット11と、周波数偏差をなくすために発振源22に印加される電圧値の指標を示す調整基準値を記憶するRAM17と、周波数偏差tfが閾値Bを超えた場合、調整基準値を用いて、基準信号の周波数を補正し、且つ、周波数偏差tfが閾値Bを超えない場合、周波数偏差tfをなくすような電圧値を基準信号発振部に印加することで前記基準信号の周波数を繰り返し補正する制御ユニット11と、を備える。

(もっと読む)

クロック発生装置およびクロック発生装置におけるジッタ低減方法

【課題】よりジッタの少ないクロック信号を発生させること。

【解決手段】周期信号を発生するDDS回路と、入力信号と基準信号とを比較して2値化信号を出力するコンパレータと、を有し、前記DDS回路において発生される前記周期信号に対し、前記基準信号との交差点における変化率を増加させる補正を行う変化率補正手段を備えることを特徴としている。

(もっと読む)

81 - 90 / 247

[ Back to top ]