国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

101 - 110 / 173

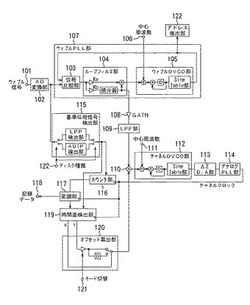

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

記録再生装置及び記録再生方法

【課題】回路規模や消費電力を増大させることなく、記録クロック及び再生クロックを安定して生成できるようにする。

【解決手段】ディスク状記録媒体に形成されたウォブル信号を検出するウォブル信号検出手段と、前記ウォブル信号検出手段によって検出されたウォブル信号に基いて、ウォブル周期に関連した周波数を有する第1のクロックを生成する第1のクロック生成手段と、前記第1のクロック生成手段が前記第1のクロックを生成する際の制御信号に予め設定された処理が施された周波数成分を制御信号とし、チャネル周期に関連した周波数を有するチャネルクロックを生成する第2のクロック生成手段とを有し、前記第1のクロック生成手段に組み込む電圧制御発振器と、前記第2のクロック生成手段に組み込む電圧制御発振器とを同一の構成にする。

(もっと読む)

情報再生装置

【課題】PLLループディレイを増加させることなく、CAV再生時にも安定的に情報を検出できる情報再生装置を提供する。

【解決手段】A/D変換器101は、固定周波数のシステムクロックsclkで読出し信号をサンプリングし、A/D変換を行う。変動補償器102は、内部帰還形の補償フィルタとして構成され、A/D変換器101が出力するデジタル信号の変動を抑圧する。デジタルPLL103は、補間器131により、チャネル周波数に同期したタイミングにおける読出し信号のサンプリング値を補間生成し、NCO134により、同期クロックと補間器131に帰還する補間位相信号とを生成する。2値化回路104は、補間器131が出力する補間値に基づいて読出し信号を2値化する。変動補償器102の周波数特性は、ループフィルタ133が出力する周波数値に基づいて制御される。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

PLL回路

【課題】帰還ループに遅延回路を挿入することなく、出力信号でのジッタの発生を抑制し得るPLL回路を提供する。

【解決手段】基準信号ref−CLKと帰還信号の位相を比較する位相比較器2と、チャージポンプ4と、ループフィルター5と、電圧電流変換器6と、電流制御発振器7aと、電流制御発振器の出力信号を分周して帰還信号を生成する分周器3とを備えた帰還ループにより、出力信号out−CLKの周波数を基準信号で設定される周波数に収束させるPLL回路であって、電流制御発振器7aから負荷回路8に出力される出力信号out−DLと位相比較器2に入力される基準信号の位相をずらす遅延回路11aを帰還ループ外に備えた。

(もっと読む)

ジッタ発生装置

【課題】ジッタをデジタル的に発生させることにより、ジッタに関する調整が可能でありジッタ非注入時の信号劣化が生じることを防止したジッタ発生装置を提供する。

【解決手段】本実施の形態におけるジッタ発生装置では、第2カウンタ5が出力する−1〜1の範囲内のランダムな整数値のカウンタ値を第1カウンタ2が出力するカウンタ値に加算して、波形メモリ3にアドレスとして入力し振幅データから波形を得ることにより、ジッタをデジタル的に発生させ、波形20に対して波形21,22の波形の間をランダムにゆらいだ、ジッタが注入された波形を得ることが可能となる。

(もっと読む)

PLL回路、位相制御方法、および、ICチップ

【課題】クロック周波数を上げることなく、受信精度を向上させる。

【解決手段】分周器131は、クロック信号f_clkを8分周することにより、PSK変調されたデジタル信号DATAとほぼ同じ周波数の互いにπ/2だけ位相が異なる信号sin(wt)、信号cos(wt)を生成する。ACT136は、信号sin(wt)および信号cos(wt)を仮想的に制御角Φだけ移相させた信号と信号DATAとの位相を比較した結果を示す信号ΣV11および信号ΣV12に基づいて、信号DATAと仮想の信号sin(wt+Φ)の位相を同期させるように、cosΦに対応するパラメータcos_paraおよびsinΦに対応するパラメータsin_paraの値を制御する。また、ACT136は、信号ΣV11およびΣV12に基づいて、CPUが信号DATAからデータを読み出すタイミングを制御する。本発明は、非接触ICチップに適用できる。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

GPS機器用の非常に精密で温度に依存しない基準周波数を生成するためのシステム及び方法

【課題】 二連式水晶発振器を組み込んだ、水晶振動子を用いたクロック発振器において温度を補償するための機器及び方法である。

【解決手段】 二つの発振器の同期を担当するプロセッサの効率的な使用によって、最小限の電力消費が達成される。この発明は、特に、携帯式無線位置測定機器に精密な基準クロックを供給するのに適している。

(もっと読む)

デジタルPLL回路およびデータ再生装置

【課題】回路規模の増大を抑制しながら、異なるPRMLに円滑に対応し得るデジタルPLL回路およびそれを採用するデータ再生装置を提供する。

【解決手段】PR(1,2,2,2,1)に従うデータ補間回路104の他にPR(1,2,2,1)に従うデータ補間回路110を配する。データ補間回路104には、デジタルVCO109によって生成されたPR(1,2,2,2,1)に従う位相情報が供給される。データ補間回路110には、デジタルVCO109によって生成された位相情報の位相を180°遅延させた位相情報が供給される。データ補間回路110に供給される位相情報は、位相調整回路113によって生成される。この構成によれば、デジタルVCO109からの位相情報をもとにデータ補間回路110のための位相情報が生成されるため、別途、データ補間回路110のためのPLL回路を配する必要がない。

(もっと読む)

101 - 110 / 173

[ Back to top ]