国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

11 - 20 / 173

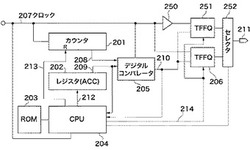

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

11 - 20 / 173

[ Back to top ]