国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

51 - 60 / 173

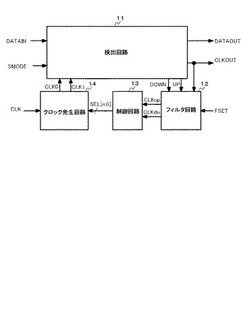

クロックデータリカバリ回路

【課題】簡単な回路で高データレートおよび低データレートに対応させる。

【解決手段】クロック信号CLK0、CLK1のエッジに係るタイミングt1、t2、t3(ただし、t2<t1<t3)でサンプリングした入力データ信号DATAINの論理値をそれぞれD1、D2、D3とする時、D1≠D2であるか、D1≠D3であるかを検出する検出回路11と、検出回路11の検出結果に基づいて、入力データ信号DATAINの論理値の遷移タイミングがタイミングt2、t3に一致するようにクロック信号CLK0、CLK1の位相を変化させるクロック発生回路14と、を備える。

(もっと読む)

2ポイント変調と適応遅延マッチングとを用いるデジタル位相ロックドループ

適応遅延マッチングとともに2ポイント変調をサポートするデジタル位相ロックドループ(DPLL)が記述される。DPLLは、それぞれ、発振器の周波数および/または位相の広帯域および狭帯域の変調をサポートするハイパスおよびローパス変調パスを含む。DPLLは、他の変調パスの遅延と合わせるためにある変調パスの遅延を適応して調整することができる。ある設計において、DPLLは、2つの変調パスのうちの一つに、可変遅延を提供する適応遅延ユニットを含む。適応遅延ユニット内で、遅延計算ユニットは、2つの変調パスに適用される変調する信号と、DPLLにおける位相エラー信号とに基づいて、可変遅延を決定する。補正器は可変遅延の小数部分を提供し、プログラマブル遅延ユニットは可変遅延の整数部分を提供する。 (もっと読む)

ディスプレイ駆動装置

【課題】本発明は、ディスプレイ駆動装置に関する。

【解決手段】本発明はディスプレイ装置、特にディスプレイ装置に使用されるバックライトユニット駆動装置において、映像信号が正常である場合には映像信号の周波数に同期された周波数を有する駆動信号を提供し、映像信号が異常状態である場合には予め設定された周波数を有する駆動信号を提供して、安定的な動作を行うため、入力された映像信号の周波数と分周された駆動信号の周波数の差を検出する周波数検出部と、上記周波数検出部からの検出結果により、上記映像信号の周波数と同期された周波数を有する上記駆動信号を生成する駆動信号生成部と、上記周波数検出部からの上記検出結果が異常動作である場合、上記周波数検出部の周波数検出動作を停止させる制御部とを含むディスプレイ駆動装置を提供する。

(もっと読む)

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

情報システムおよび半導体装置とその制御方法

【課題】周期の小さいジッタに対する低減効果を向上する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路14を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路14における遅延量を制御する。位相補正回路21は、入力クロック信号CLKiおよび出力クロック信号CLKoを入力とし、DLL回路がロック状態に入った後に、入力クロック信号CLKiおよび出力クロック信号CLKoの位相がずれた場合に、出力クロック信号CLKoの位相に基づいて入力クロック信号CLKiの位相に補正を加え、電圧制御遅延回路14に出力する。

(もっと読む)

DLL回路とその制御方法

【課題】安定的にジッタを低減する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路12を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路12における遅延量を制御する。位相比較結果判定回路15は、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果を所定の期間に亘って積算し、積算結果の分布に基づいて遅延量を制御する。

(もっと読む)

同期検出回路、これを用いたパルス幅変調回路、及び同期検出方法

【課題】部品点数の削減、高い検出精度の確保、処理速度低下の防止等を図る。

【解決手段】位相ロックループ回路15により、基準クロック信号に基づいて互いに位相が異なる複数相の多相クロック信号を生成する多相クロック生成回路11と、前記多相クロック信号の中から、同期信号に同期するクロック信号を特定する同期クロック特定回路12とを有する同期検出回路2であって、前記多相クロック生成回路11は、前記基準クロック信号を逓倍した周波数を有する高速多相クロック信号と、前記高速多相クロック信号を分周した周波数を有する低速多相クロック信号とを生成し、前記同期クロック特定回路は、同期信号と前記高速多相クロック信号との比較結果と、前記同期信号と前記低速多相クロック信号から選択された代表クロック信号との比較結果とに基づいて、前記同期信号の同期位置を示す同期位置信号を生成する。

(もっと読む)

発振回路、DC−DCコンバータ及び半導体装置

【課題】CPUなどの特別な制御回路が不要で、しかも無線送受信回路で用いている周波数に関わりなく、スイッチングノイズの影響を無視できるレベルまで軽減することが可能な発振周波数制御回路を提供する。

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

(もっと読む)

同期化制御回路、半導体装置及び制御方法

【課題】従来の回路に比較し、面積の縮小や消費電力の低減を図ることができる同期化制御回路を提供する。

【解決手段】分周回路部26において、外部クロックに対し位相の進んだ内部クロックLCLKを分周して分周クロックRSELOを生成し、分周クロックRSELOを遅延させて遅延分周クロックRSELIを生成する。外部クロックに対し位相の遅れた内部クロックPCLKに同期して外部から取り込まれた信号を、遅延分周クロックRSELIに同期してラッチ回路22に保持する。次いで、ラッチ回路22の出力信号を分周クロックRSELOに同期してラッチ回路23に読み込み、内部クロックLCLKに同期した信号として出力する。そして、分周回路部26が、変更可能な所定の分周数で内部クロックLCLKを分周する可変分周回路24を備える。

(もっと読む)

51 - 60 / 173

[ Back to top ]