国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

1 - 10 / 119

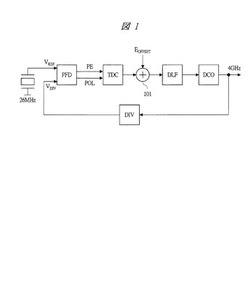

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

(もっと読む)

PLL回路

【課題】本発明は、遅延素子の遅延時間のばらつきを補償するように、デジタルコードを補正する必要のないTDCを提供することを目的とする。

【解決手段】基準信号の周波数に対して所望倍数の周波数を有する出力信号を出力する発振部と、基準信号についての出力信号の整数分周及び小数分周の和並びに当該所望倍数について差分を計算し、発振部に当該差分を0にするように出力信号を出力させる位相比較部と、を備えるPLL回路において、TDC2は、小数分周の初期値を設定し、初期値を計測値として出力するデジタルコード発生器23と、初期値に基づく位相比較部及び発振部の動作後に、当該差分を0にする方向に、小数分周の分解能を1ステップとして段階的に、小数分周を初期値から最適値へと更新し、最適値を計測値として出力するデジタルコード発生器23及び加減算器24と、を備える。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

【課題】デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作を提供する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

(もっと読む)

CDR回路

【課題】線形位相比較器を用いながら、チャージポンプやVCO等のアナログ回路を不要とすることができ、回路面積を抑えたCDR回路を提供する。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

1 - 10 / 119

[ Back to top ]