国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

101 - 110 / 172

PLL回路

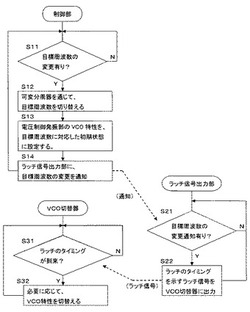

【課題】目標周波数の変更に応じて、制御電圧が所定の許容範囲内に収まるようにVCO特性が切り替えられるものであって、かかる切替を極力早いタイミングで実行し得るPLL回路を提供する。

【解決手段】複数のVCO特性に切替可能である電圧制御発振部と、位相比較器と、制御電圧と所定の許容範囲との比較結果に応じてVCO特性の切替を行うVCO切替部と、を備え、現時点で目標周波数に設定されている周波数のクロックを出力するPLL回路であって、VCO切替部は、サンプリングされた電圧が許容範囲内に収まっているか否かを検出するとともに、該検出結果に応じて、前記VCO特性の切替えを行うものであり、このサンプリングのタイミングは、目標周波数が切り替えられた時から、予め定められた時間である第1時間が経過したタイミングとされているPLL回路とする。

(もっと読む)

クロック監視回路及びルビジウム原子発振器

【課題】互いに相手のクロックを監視することができるようにして、簡単な回路構成で確

実にクロック停止を監視することができるクロック監視回路を提供する。

【解決手段】このクロック監視回路60は、異なる発振源から発振された2つのクロック

CLK−A、CLK−Bの何れか1つのクロックが停止したことを検出するクロック監視

回路であって、各発振源から発振された夫々のクロックCLK−A、CLK−Bを計数す

るカウンタA、カウンタBと、各カウンタA、Bが所定の計数値を計数したことを検出す

る検出回路A、検出回路Bと、を備え、夫々のカウンタA、Bをリセットするリセット端

子Rには、当該カウンタを歩進させるクロック以外のクロックを接続するものである。例

えば、カウンタAのリセット端子Rには、CLK−Bを接続し、カウンタBのリセット端

子Rには、CLK−Aを接続する。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

デューティサイクル補正機能を有する遅延ロックループ回路およびその制御方法

【課題】PVT変動が発生しても安定して正確な遅延ロックおよびデューティサイクル補正を可能とする。

【解決手段】外部クロックが入力されて第1内部クロックを生成し、前記第1内部クロックを内部の遅延手段によって遅延して複数の第2内部クロックを出力した後にフィードバックを受けて、前記第1内部クロックとの位相差によって前記遅延手段の遅延時間を調整することにより、前記第2内部クロックの遅延ロックがなされるようにする遅延ロックループブロックと、前記複数の第2内部クロックのデューティサイクルを補正したデューティサイクル補正クロックを出力するデューティサイクル補正ブロックと、前記複数の第2内部クロックの位相比較結果に応じてデューティ補正エラーの発生を判断して、前記デューティサイクル補正クロック又は前記複数の第2内部クロックのうちの1つを前記遅延ロックループブロックにフィードバックするエラー判断部とを備える。

(もっと読む)

無線受信装置及び無線受信方法

【課題】発振信号の生成が安定する前に電力が無駄に消費されていた。

【解決手段】無線受信すべき信号を処理するための発振信号の周波数を指定する指定回路と、前記指定された周波数を有する前記発振信号を生成するPLL回路と、前記発振信号が安定しているときに行うべき第1の動作、及び、前記発振信号が安定していないときに行い得る第2の動作であって消費電力が前記第1の動作より小さい前記第2の動作に選択的に切り換わる動作切換回路と、前記PLL回路が前記発振信号の前記周波数の指定を受けたときから当該PLL回路による当該発振信号の生成が安定するまでの期間、前記動作切換回路を前記第2の動作に設定し、前記PLL回路による前記発振信号の生成が安定した後、前記動作切換回路を前記第1の動作に設定する制御回路と、を含む。

(もっと読む)

位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測のための装置。

【課題】 位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測の方法及び装置を提供する。

【解決手段】 装置は、位相誤差信号を出力するように構成された位相・周波数検出器を含む位相ロック・ループPLL回路(100)を含む。位相誤差モニター回路(102)は、位相誤差信号を論理的に結合し、論理的に結合された位相誤差信号のパルス幅を各基準クロック・サイクルにおいてプログラム可能な遅延時間と比較して瞬時位相誤差変化を決定することにより、瞬時ピーク位相誤差を決定するように構成される。記憶素子(124)は瞬時位相誤差変化をストアするように構成される。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、高安定な基準信号の入力がなく、自走したときでも発振周波数を安定に保つことができる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、外部基準信号を検波する検波回路17と、パルス生成の情報が入力されるとパルスを生成してループフィルタ14に出力するPWM回路22と、電圧情報と対応するパルス生成の情報を記憶するメモリ21と、位相比較器12とループフィルタ14との接続をオン/オフするスイッチ13と、検波回路17で検出された外部基準信号のレベルが適正範囲内であればスイッチ13をオンとし、レベルが適正範囲外であればスイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する発振周波数制御回路である。

(もっと読む)

PLL同期はずれ検出回路

【課題】電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、PLL同期はずれ検出回路の検出精度を向上させることを目的とする。

【解決手段】基準クロックと電圧制御発振器3の出力クロックの位相を比較して位相差に対応する信号を出力する位相比較器1と、位相比較器の出力により出力クロックの周波数を調整する電圧制御発振回路を有し、電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、時間を計測するタイマ6と、電圧制御発振器の出力クロックをカウントし、タイマからの信号でリセットされるカウンタ5と、カウンタのカウントした値が判定値を超えると信号を出力し、電圧制御発振器の出力クロック周波数増加方向の同期はずれを検出する検出器とを備える。

(もっと読む)

PLL回路とPLL回路の電圧制御発振器に供給する制御電圧の制御方法およびプログラム

【課題】 同一のRF周波数で複数の送信所から同一時間、同一内容の電波を送出するSFN(SINGLE FREQUENCY NETWORK)が構築される地上デジタル放送方式においては、受信が重なり合うエリアでは送信信号のFFTクロック精度や送信タイミングにずれが発生すると受信不能(SFNの破綻)が発生する。

【解決手段】 外部同期クロックのエラーを検出した時、正常時トレースし記録しておいた制御電圧を元に、制御電圧の外部同期クロックに対する変化の傾向を計算により推測し、推測し計算した制御電圧を電圧制御発振器に供給する制御電圧とする。

(もっと読む)

PLLロック検出回路および半導体装置

【課題】高精度のPLLロック検出信号を得るとともに、平滑回路を削除することができるPLLロック検出回路を提供する。

【解決手段】本発明に係るPLLロック検出回路は、PLL回路において、誤ってロック判定することなく、安定したロック状態においてロック判定とアンロック判定の両方を同時に行うことにより、確実なロック判定を行う。PLLロック状態が数H連続して継続しているかどうかの検出を行う連続性検出部と、PLLアンロック状態が数H連続して継続しているかどうかの判定行う連続性検出部を備え、これら連続性検出部によってPLLのロック状態が同時に検出され、その検出結果を保持するR−Sラッチ部を備えている。

(もっと読む)

101 - 110 / 172

[ Back to top ]