国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

41 - 50 / 172

遅延同期ループ回路

【課題】外部クロック信号が擾乱したとき、擬似ロックを検出し初期化したとき、電源を投入したとき、いずれの場合も確実にロックはずれを防止でき、レイアウトがコンパクトなDLL回路を提供する。

【解決手段】遅延同期ループ回路であって、入力クロックを、制御電圧の大きさに応じて遅延させて帰還クロックを出力する電圧制御遅延手段と、帰還クロックと基準クロックとを比較して位相差を検出し、該位相差に応じて、制御電圧を上昇させるための上昇信号と該制御電圧を下降させるための下降信号とを出力する位相比較器と、上昇信号と下降信号とに応じて制御電圧を決定し、電圧制御遅延手段に出力する制御電圧生成手段と、基準クロックと電圧制御遅延手段からの中間クロックとの論理和に基づき位相比較器をリセットする。

(もっと読む)

PLL回路

【課題】 エージング特性を自動補正し、外部基準信号の未接続又はアンロック時に出力周波数変動を小さくできるPLL回路を提供する。

【解決手段】 基準信号が適正範囲内でロック状態の場合に、初期調整時に、チャージポンプ出力電圧(A)の初期電圧を温度情報Tと共に読み取り、自走周波数設定用電圧(B)が電圧(A)となるようのDAコンバータ又はPWM出力回路9の設定値を調整し、温度特性初期テーブルを生成し、運用中に、温度情報Tにおける電圧(A)の最新電圧に対応する設定値を、温度特性初期テーブルを参照して特定し、初期電圧と最新電圧の設定値の差分で当該テーブルをオフセット補正して自走用温度補正テーブルを生成し、アンロック状態等になると特定された設定値による自走周波数設定用電圧(B)で自走するPLL回路である。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

PLL回路

【課題】基準周波数信号がPLL回路に入力されなくなった場合に、チャージポンプ回路にループフィルタから電流が流れ続けることを防止する。

【解決手段】PLL回路1は、入力された電圧に応じた周波数のVCO信号を出力するVCO20と、入力された電流に応じた電圧をVCO20に与えるループフィルタ18と、第一入力信号と第二入力信号との位相差に応じた幅の位相差パルスを出力する位相比較器14と、位相差パルスを受けて、ループフィルタ18への電流入力を行うチャージポンプ回路16と、REF信号(基準周波数信号)が入力されていない無入力状態において、チャージポンプ回路16への位相差パルスの入力を停止させる位相差パルス停止部30とを備える。なお、第一入力信号は、REF信号自身又はそれを分周した信号であり、第二入力信号は、VCO信号自身又はそれを分周した信号である。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

局部発振器を調整する装置及び方法

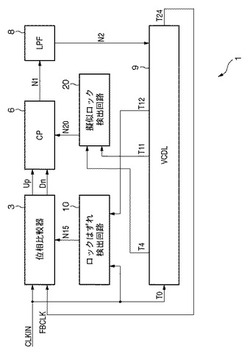

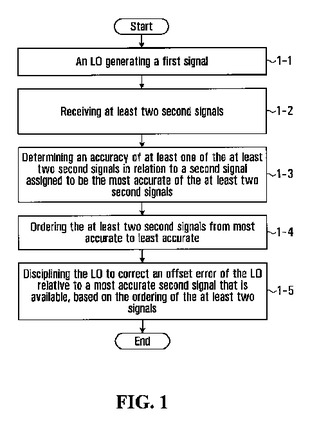

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

測定装置、再生装置、測定方法

【課題】PLL回路をより的確に評価できるPLL性能測定装置を提供する。

【解決手段】フェーズロックドループ回路にて検出される位相誤差についての移動平均を求める。この移動平均と閾値との比較に基づいて、フェーズロックドループ回路がロック状態に収束したか否かの判定を行う。

(もっと読む)

PLL回路

【課題】本発明の課題は、PLL回路のリファレンスリークと位相雑音を低減することである。

【解決手段】チャージポンプ回路14は、ロック状態監視回路19から出力される、PLL回路11がロック状態か否かを示す信号に基づいてチャージポンプ電流を切り換える。PLL回路11がアンロック状態のときには、第1及び第2の電流供給回路からチャージポンプ電流を供給し、ロック状態となると、第2の電流供給回路からのみチャージポンプ電流を供給する。

(もっと読む)

41 - 50 / 172

[ Back to top ]