国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

61 - 70 / 172

位相同期回路

【課題】 簡単な構成で、暴走状態に陥る前により確実に異常を検知し、半導体装置の誤動作をより効果的に防止できる位相同期回路を提供する。

【解決手段】 発振制御回路11、電圧制御発振回路12、帰還回路13を備え、発振制御回路11の出力電圧、発振制御に係る発振制御回路11及び電圧制御発振回路12のアナログ内部電圧の内、少なくとも何れか1つの電圧を異常検出用電圧Vdi(i=1〜n)とし、異常検出用電圧Vdiがロック可能範囲の上限値より高く設定された第1判定電圧Vri1より高い場合または下限値より低く設定された第2判定電圧Vri2より低い場合に異常状態であると判定する異常判定回路15iが、異常検出用電圧Vdi夫々について各別に設けられ、異常判定回路15i夫々における異常状態の検出結果を用いて暴走前状態であるか否かを判定し、暴走前状態であると判定した場合に、初期化動作を行う異常復帰回路16を備える。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

DLL回路、PLL回路

【課題】ロックイン時間を短縮しつつチャージポンプ回路の誤差電流に起因するジッタを低減する。

【解決手段】チャージポンプ回路30は、位相比較回路20による比較結果(充電信号UP0,放電信号DN0)に応答して正または負の出力電流Ioutを出力する。電流制御回路11は、遅延クロックCK(n)の遷移エッジを含む有効期間中に遅延クロックCK(1)の遷移エッジが発生することを検出し、その検出結果に応じてチャージポンプ回路30の出力電流Ioutの電流量を制御する。

(もっと読む)

基準信号発生装置

【課題】、目的周波数の基準信号の異常を、確実且つ正確に検出することができる基準信号発生装置を実現する。

【解決手段】基準信号発生装置1は、位相比較器11、ループフィルタ12、電圧制御発振器13、分周器14からなるPLL回路を備える。基準信号発生装置1の波数計測部15は、PLL回路の調整用タイミング信号に基づく期間での復調用基準周波数信号の波数をカウントし、期間毎のカウント値を異常発振検出部16へ出力する。異常発振検出部16は、調整用タイミング信号の元となる基準信号と復調用基準周波数信号との仕様周波数範囲の関係に基づいて設定される正常発振カウント値範囲を予め記憶している。異常発振検出部16は、波数計測部15から取得したカウント値が正常発振カウント値範囲内に無ければ異常発振として検出し、外部へ通知する。

(もっと読む)

周波数シンセサイザ

【課題】電圧制御発振部からの周波数信号を分周、A/D変換、直交検波を行い、検波に用いた周波数信号とA/D変換した周波数信号との周波数差で回転する回転ベクトルを取り出し、この回転ベクトルの周波数と設定周波数との差分を積分して電圧制御発振部の制御電圧とする周波数シンセサイザにおいて、PLL制御が正常に動作しない状態を瞬時にあるいは事前に判定できる技術の提供。

【解決手段】電圧制御発振部に入力される制御電圧を監視し、監視された制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断してアンロック検出信号を出力する。回転ベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算して回転ベクトルを減速する構成においては、減速された回転ベクトルの長さ(スカラー量)またはゲイン制御用の補正信号が予め設定した範囲から外れているか否かの判定結果を更に考慮する。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

基準信号発生装置

【課題】起動からホールドオーバが起きるまでのタイミングによらず、高精度な自走用制御電圧信号を出力する。

【解決手段】基準信号発生装置は、起動して1PPSを受信すると、同時に自装置内のPLL回路の制御電圧信号のDAC値を順次記憶する。基準信号発生装置は、制御値変化量算出タイミングになると、当該タイミングの直前の期間でのDAC値の変化量である制御値変化量を算出する。基準信号発生装置は、このようなタイミングでの制御値変化量の算出を二回行うと、隣り合う期間の制御値変化量の差分値を算出し、当該差分値が推定利用可能閾値レベルと比較する。基準信号発生装置は、差分値が推定利用可能閾値レベル以下であることを検出すると、このタイミングの直前の期間のDAC値から自走用制御電圧信号の推定を開始し、それ以前の期間のDACを利用しない。この処理は、推定開始の判断がされるまで繰り返し行われる。

(もっと読む)

半導体集積回路

【課題】入力された信号の位相と内部クロック信号の位相との差を所定の範囲内で吸収する能力を正確に試験することができる半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力された信号の位相によって制御された位相を有する信号を生成する信号生成回路と、制御値を生成する制御値生成ブロックとを備えており、制御値生成ブロックが生成した制御値に応じて信号生成回路が生成する信号の位相を強制的にずらすことによって信号生成回路を試験する。ここで、制御値生成ブロックは、内部クロック信号に同期して動作するとともに、外部から、内部クロック信号よりも低い周波数を有する外部クロック信号に同期して目標値を受信し、受信した目標値に基づいて、内部クロック信号に同期して変化する制御値を生成する。

(もっと読む)

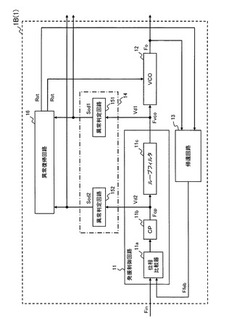

位相同期回路、情報再生装置、電子機器、位相同期回路のゲイン制御方法

【課題】PLLゲインを自動制御してキャプチャ時間の短縮やエラーレートの改善を実現するに当たり、ロック判定の手法として種々の方法を提案する。

【解決手段】媒体再生時のPLL動作時に、PLLロック状態を示す情報を用いてPLLゲインを切り替えることでロバストなPLLを実現する。PLLロック状態の検出は、フレームシンクの検出結果、位相誤差の絶対値の積算量、の何れかを評価指標として測定し、一定区間での当該評価指標の大小を判定し、判定結果に基づき位相同期ループがロックしているか否かを示すRF品質信号RQを生成する。フレーム同期信号の検出間隔を監視し、その監視結果に基づきRF品質信号RQを生成するとよい。RF品質信号RQは、概ねPLLがロック時はH、アンロック時はLとなる。RF品質信号RQがHレベルの区間では低倍率となり、RF品質信号RQがLレベルの区間では高倍率となるように、PLLゲインを制御する。

(もっと読む)

61 - 70 / 172

[ Back to top ]