国際特許分類[H03L7/16]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/16]の下位に属する分類

ループの中に分周器または計数器を用いるもの (427)

高調波位相ロックループ,すなわち供給された多数の高調波関係にある周波数の内の一つにロックされることができるループを用いるもの

二つ以上のループを用いるもの (73)

国際特許分類[H03L7/16]に分類される特許

1 - 10 / 28

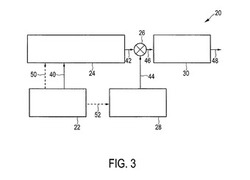

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

信号レベル調整装置及び高周波機器

【課題】電圧制御発振器の後段に設けられた可変減衰器と、検波器と、検波電圧に応じてディジタル/アナログ変換器を介して可変減衰器の減衰量調整用の制御電圧を出力する制御部と、を備えた周波数シンセサイザにおいて、ディジタル/アナログ変換器の出力変化に基づくスプリアスを抑制できる技術を提供すること。

【解決手段】ディジタル/アナログ変換器の出力側と可変減衰器との間にローパスフィルタを設けて、ディジタル/アナログ変換器の出力の変化時に発生するオーバーシュートに対応する周波数成分をカットする。そして制御部が制御電圧を出力してから検波器で検出された信号レベルを読み込むまでの時間は、ローパスフィルタのカットオフ周波数で決まる当該ローパスフィルタの時定数よりも長い時間に設定し、信号レベルの自動制御動作に影響がないようにする。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

発振器

【課題】フロア雑音または位相雑音を抑えることができ、かつ分周器の分周比の設定に手間がかからない発振器を提供すること。

【解決手段】周波数シンセサイザの出力信号を順次分周する複数の分周器と、前記複数の分周器における最終段の分周器から目的とする周波数が得られるように、当該複数の分周器の各々について、入力周波数と分周比との組み合わせを複数設定すると共に各組み合わせ毎に、各段の分周器の出力信号のフロア雑音または位相雑音の大きさを記載した分周特性データを記憶する記憶部と、前記記憶部に記憶されている分周特性データに基づいて、各分周器の許容入力周波数の範囲内でありかつ最終段の分周器からの出力信号のフロア雑音または位相雑音が良好な入力周波数と分周比との組み合わせを判断して選択する選択部と、を備えるように発振器を構成する。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

PLL回路

【課題】PLL回路の不安定状態や位相雑音特性の劣化を回避する。

【解決手段】

発振周波数が電圧制御発振器からのフィードバック信号と外部から入力される基準信号との位相差に応じて制御されるPLL回路において、前記フィードバック信号を分周する分周器と、前記基準信号を逓倍する逓倍器と、前記分周器からの出力信号と前記逓倍器からの出力信号とをミキシングし周波数変換するミキサと、前記ミキサからの出力信号を分周しデジタル分周信号を出力する第一のデジタル分周器と、前記基準信号を分周しデジタル分周信号を出力する第二のデジタル分周器と、前記第一のデジタル分周器からのデジタル分周信号と、前記第二のデジタル分周器からのデジタル分周信号とを、デジタル位相比較する位相比較器と、を備える。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

周波数出力装置の内部基準信号源を校正する方法

【課題】簡便な手法で正確な校正を行うことが可能な周波数シンセサイザの内部基準信号を校正する方法を提供する。

【解決手段】基準クロック信号と周波数設定信号とに基づいて、設定された周波数信号を出力する周波数シンセサイザ1の、前記基準クロック信号を出力する内部基準信号源16を校正する手法において、前記周波数シンセサイザ1を周波数設定信号に基づいて動作させ、その出力周波数を周波数測定装置3により測定する工程と、測定された出力周波数と前記周波数設定信号により決定される周波数設定値との周波数差に基づいて、外部制御機器2により、周波数シンセサイザ1の不揮発性メモリ17に記憶されている指令値を増減して最適な指令値とする工程と、を含む。

(もっと読む)

1 - 10 / 28

[ Back to top ]