国際特許分類[H04L9/10]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | 秘密または安全な通信のための配置 (13,382) | 特別な箱体,構造的特徴または手動制御装置を有するもの (818)

国際特許分類[H04L9/10]に分類される特許

31 - 40 / 818

画像処理装置、及びその制御方法

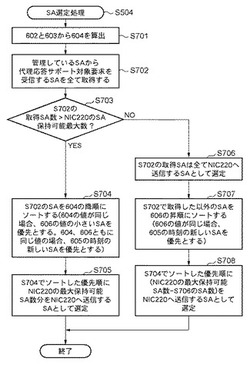

【課題】省電力モード時に動作する制御部のリソースが、通常電力モード時に動作する制御部のリソースよりも少ない場合であっても、好適に省電力モードを維持するとともに、省電力モードにおいてセキュリティ通信を実現する画像処理装置、及びその制御方法を提供する。

【解決手段】本画像処理装置は、第1の電力モード及び該第1の電力モードよりも消費電力の小さい第2の電力モードを有し、装置全体を制御する第1制御部と、第1の電力モード及び第2の電力モードにおいて電力が供給される第2制御部とを備え、外部装置とセキュリティ通信を実行する。また、第1制御部は、第1の電力モードから第2の電力モードへ移行する際に、セキュリティ通信に関連する複数のセキュリティ関連情報を記憶する記憶部に記憶された複数のセキュリティ関連情報から第2制御部に通知するセキュリティ関連情報を選定する。

(もっと読む)

物理乱数発生器

【課題】高速の物理乱数を安定に発生する物理乱数発生器を提供する。

【解決手段】周期パルスが入力され、遅延時間揺らぎを有する出力信号を出力する第1の遅延回路と、該第1の遅延回路の前記出力信号が入力される第1入力端及び他の信号が入力される第2入力端を有し、前記第1入力端及び前記第2入力端へ入力される信号の到達時刻の時間差に応じて“1”または“0”の信号を確率的に出力する論理回路とを備えた物理乱数発生器であって、前記他の信号と前記周期パルスとは同期関係を有し、前記論理回路は、前記出力信号の到達時刻と前記他の信号の到達時刻との時間差が所定の値(反応時間差:Th)のときに確率50%で“1”の信号を出力する。

(もっと読む)

データ処理装置、およびデータ処理方法、並びにプログラム

【課題】小型化した非線形変換部を実現する。

【解決手段】データ処理対象となるデータの構成ビットを複数ラインに分割して入力し、各ラインのデータに対してラウンド関数を適用したデータ変換処理を繰り返して実行する暗号処理部を有し、暗号処理部は、複数ラインを構成する1ラインのデータを入力して、変換データを生成するF関数実行部を有し、F関数実行部は非線形変換処理を実行する非線形変換処理部を有し、非線形変換処理部は1つのNANDまたはNOR演算部と、1つのXORまたはXNOR演算部からなる非線形演算部と、ビット置換部との繰り返し構造を有する。この繰り返し構成により小型化された非線形変換部を実現する。

(もっと読む)

検証サーバ、プログラム及び検証方法

【課題】 HSMを用いる検証サーバにおいて、検証要求を受け付けてから検証結果を応答するまでの時間を短くし、検証サーバの処理性能を向上すること。

【解決手段】 HSMがI/F部148に接続されている検証サーバ130に、第一のソフトウェア暗号モジュール142と、第二のソフトウェア暗号モジュール143と、を備えておき、HSM、第一のソフトウェア暗号モジュール142及び第二のソフトウェア暗号モジュール143の負荷状態を暗号モジュール監視部141で監視し、証明書の検証処理において暗号演算を行う際には、暗号モジュール選択部140において負荷が最もかるい暗号モジュールをこれらのなかから選択して、暗号演算を行う。

(もっと読む)

機密データの暗号化および記憶

【課題】機密データをセキュアに記憶するためのデータ記憶回路、およびデータを処理および記憶するためのデータ処理装置、ならびに方法を開示する。

【解決手段】データ記憶回路は、データを記憶するための複数のデータ記憶場所を備える、データ記憶と、データ記憶にアクセスするための要求を受信するための入力と、データ記憶内の物理データ記憶場所へのアクセス要求に指定されたアーキテクチャデータ記憶場所をマッピングするためのリネーミング回路と、データ記憶内へのデータの記憶に先立って、データを暗号化するための暗号化回路であって、その中にデータが記憶される物理データ記憶場所に応じて、暗号化キーを生成するように構成される、暗号化回路と、データ記憶から読み取られたデータを復号するための復号回路であって、そこからデータが読み取られる物理データ記憶場所に応じて、復号キーを生成するように構成される、復号回路と、を備える。

(もっと読む)

インターフェース回路および画像形成装置

【課題】外部記憶メディアの状態にかかわらず暗号器の正当性の確認を行うことができるようにする。

【解決手段】暗号器153に対するテストモードを設定するモード選択部171と、テストモード中のDMAコントローラ152の動作を制御するDMAコントローラ制御部174と、テストモード中の暗号器153の動作を制御する暗号器制御部173とを有し、テストモード時に暗号器153を通してメモリとSRAM151との間でテストデータの読み取り、書き込みを往復で行うようにDMAコントローラ152の転送方向を切り替え制御して暗号器153の暗号化、復号に関するテストを行わせるテスト回路170を備える。

(もっと読む)

半導体集積回路

【課題】記憶装置に記憶された機密データが容易に改ざんされたり読み出されたりすることを防止することが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路10は、複数のCPU暗号キーを格納するCPU暗号キー格納部60と、複数のCPU暗号キーのうち何れかのCPU暗号キーをCPU暗号キー格納部60の中から選択して出力するCPU30と、CPU30によって選択されたCPU暗号キーと、外部から供給された外部暗号キーと、に基づいて内部暗号キーを生成する内部暗号キー生成回路40と、CPU30から出力されたアドレス信号A0〜Anを内部暗号キーに基づいて変換し、アドレス信号B0〜Bnとして出力するアドレス変換回路50と、を備える。

(もっと読む)

暗号処理プログラム、暗号処理装置および暗号処理方法

【課題】ファイルの安全性の向上を容易に実現すること。

【解決手段】暗号化手段1aは、情報処理装置2から受信した平文ファイル3を暗号化して生成した暗号化ファイル4を情報処理装置2に送信する。情報処理装置2は、暗号化ファイル4を復号して取得した平文ファイル3の補助記憶装置2aへの出力を制限して暗号化ファイル4の編集を行う。復号手段1bは、情報処理装置2から暗号化ファイル4を編集した暗号化ファイル4aを受信すると、暗号化ファイル4aを復号して平文ファイル3aを生成し、平文ファイル3に対応するファイルとして平文ファイル3aを情報処理装置2に送信する。

(もっと読む)

暗号化処理回路、及び、暗号化処理方法

【課題】外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することが可能な暗号化処理回路を提供すること。

【解決手段】暗号化処理回路100は、レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。暗号化処理回路100は、外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路101と、上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路102と、を備える。

(もっと読む)

通信装置およびセキュアモジュール

【課題】不正ソフトウェアによる正規の暗号鍵を用いた暗号化通信の防止を図ること。

【解決手段】通信装置101内のセキュアモジュール102は、暗号鍵Kをセキュアに管理している。セキュアモジュール102は、暗号化通信をおこなうプログラムの改ざんの有無を検出する。セキュアモジュール102は、改ざんされていない正規プログラムには暗号鍵Kを供するが、改ざんされた不正プログラムには暗号鍵Kを用いた暗号化通信ができないようにする。これにより、不正プログラムが送信内容を偽装したとしても、暗号鍵Kにより暗号化通信ができないため、安全な暗号化通信を担保できる。

(もっと読む)

31 - 40 / 818

[ Back to top ]