国際特許分類[H04N7/01]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | 画像通信,例.テレビジョン (280,882) | テレビジョン方式[4,2011.01] (43,981) | 標準方式の変換 (1,468)

国際特許分類[H04N7/01]に分類される特許

71 - 80 / 1,468

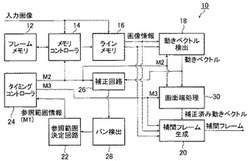

画像処理装置

【課題】従来とほぼ同等の回路および回路規模で高速なパン動画のフレーム補間を行うことができる画像処理装置を提供する。

【解決手段】画像処理装置は、現在フレームの画素データをラインの順番に受信してラインメモリに記憶し、過去フレームの画素データをラインの順番にフレームメモリから読み出してラインメモリに記憶するメモリ制御回路と、パン速度の縦方向成分に応じて定めた第1の移動量M1だけ、縦方向成分を削減した縦方向成分削減済み動きベクトルを受け取り、動きベクトルによって対応づけられる、現在フレーム画素データと過去フレーム画素データとに基づいて、補間フレームの画素データを生成する補間フレーム生成回路とを備える。メモリ制御回路は、ラインメモリに過去フレーム画素データを記憶するタイミングを、第1の移動量M1がゼロである場合の標準タイミングから、第1の移動量M1に対応する第2の移動量M2だけ移動する。

(もっと読む)

画像処理装置、画像処理方法及びプログラム

【課題】任意の倍数のフレームレート変換処理を可能とするとともに、高精度な動きベクトルの探索を行う。

【解決手段】CPUは、補間画像データ302に定義された基準位置に対応する入力画像データ301内における基準位置を基準として、第1の時刻比(1−A)を空間のずらし量を示す変数に対して乗じた位置に存在する第1のブロック505を取得する。また、CPUは、補間画像データ302に定義された基準位置に対応する遅延画像データ300内における基準位置を基準として、第2の時刻比Aを上記変数に対して乗じた位置に存在する第2のブロック503を遅延画像データ300から取得する。CPUは、所定の条件を満たす相関性にある第1のブロックと第2のブロックとが取得された際の上記変数に基づいて、補間画像データ302における動きベクトルを算出する。

(もっと読む)

映像信号処理装置及び映像信号処理方法

【課題】補間フレーム生成用の記憶容量を削減しても映像品質の低下を防ぐことができる映像信号処理装置等を提供する。

【解決手段】記憶領域4a〜4cが3個分設けられた記憶部4と、記憶領域4a〜4cをフレームごとに巡回させて原映像信号を書き込むよう制御する書き込み制御部1と、3回に亘り連続した原映像信号が供給されるフレーム位相のうち3回目のフレーム位相である場合に、記憶領域4a〜4cの巡回を停止させる書き込み停止部2と、フェイズ信号を参照して、記憶領域4a〜4cから異なる2つの映像信号を読み出すよう制御する読み出し制御部3と、読み出し制御部3の制御に従って記憶部4の記憶領域4a〜4cから読み出された2つの映像信号を用いて、動きベクトルに基づいて2つの映像信号間に挿入される補間フレームを生成する補間フレーム生成部5とを有する。

(もっと読む)

画像処理装置および方法、並びにプログラム

【課題】任意のプルダウンパターンの入力画像について、プルダウンされる前のフレーム周波数を推定する。

【解決手段】プルダウン周期検出部は、プルダウンされた入力画像におけるプルダウンパターンを検出し、フレーム周波数算出部は、プルダウンパターン、および入力画像のフレーム周波数である第1のフレーム周波数に基づいて、入力画像がプルダウンされる前の原画像のフレーム周波数である第2のフレーム周波数を算出する。本技術は、所定のプルダウンパターンでプルダウン処理が行われた入力画像をフレームレート変換する画像処理装置に適用することができる。

(もっと読む)

画像表示装置

【課題】本発明は、入力映像の種類やユーザーの希望に応じてフレーム補間を行う画像表示装置の提供を目的とする。

【解決手段】本発明の画像表示装置は、外部から入力された入力映像信号のフレームレート判定とプルダウン検出を行うフレームレート判定部5と、入力映像信号が、24フレーム/秒の映像信号から2−3プルダウン処理されたプログレッシブ信号であるとフレームレート判定部5で判定された場合に、前記プログレッシブ信号にプルダウン逆変換を行って24フレーム/秒の逆変換映像信号を出力するプルダウン逆変換部2と、外部操作入力に従い、前記入力映像信号と前記逆変換映像信号のいずれかを選択するセレクタ9と、前記セレクタ9が選択した映像信号の元フレーム間に補間フレームを挿入してフレームレートを向上するフレーム補間部4とを備える。

(もっと読む)

画像処理装置

【課題】メモリ容量を削減することができる画像処理装置を提供する。

【解決手段】画像処理装置は、複数のフレームの画素データを、フレームの順番に受信し、フレームメモリに記憶するメモリ制御回路と、フレームメモリに記憶された画素データの上位ビット部分を利用して処理済み画素データを生成する画像処理回路と、処理済み画素データを出力する出力回路とを備える。メモリ制御回路は、画素データを、上位ビット部分と下位ビット部分とに分離する分離回路と、下位ビット部分をフレームメモリに記憶する下位ビット処理回路とを含む。下位ビット処理回路は、それぞれのフレームの画素をn組(nは2以上の整数)に分割し、連続するnフレームの画素データを受信する期間に、分割したn組の画素のうちの対応する1つの組の画素の画素データのみの分離した下位ビット部分をフレームメモリに記憶する。

(もっと読む)

映像再生装置

【課題】三次元映像を再生可能な映像再生装置において、簡易な処理によって所望のシーンを滑らかに再生することが可能な映像再生装置を得る。

【解決手段】STB4は、三次元映像を再生可能な映像再生装置であって、表示画面における映像の再生を制御する映像制御部13と、フレームレートの変更を受け付けるフレームレート変更部12と、を備え、フレームレート変更部12によってフレームレートの変更が受け付けられた場合、映像制御部13は、左視用映像及び右視用映像のうち一方の対象フレームの映像に代えて、対象フレームとその次フレームとの間のフレーム間映像を表示する。

(もっと読む)

車載動画表示装置

【課題】走行中の安全性を確保しつつ、運転者にとっての娯楽性を向上させることが可能な表示制御を行う車載動画表示装置を提供する。

【解決手段】表示処理では、車両の走行状態に基づく各パラメータを取得し(S110)、車両が走行中である場合には(S120;NO)、取得した各パラメータを負荷換算テーブルに入力することにより、車両の運転に対する運転者の負荷レベルを出力し、この負荷レベルを表す運転負荷推定情報を生成する(S130)。そして、生成した運転負荷推定情報に基づいて、負荷レベルが許容レベル範囲内である場合に限り(S150;YES)、静止画コマ送り映像を表示する(S160)。これにより、運転中の動画像の表示を一律に禁止する場合と比較して、運転者の注意力が散漫にならない範囲内で、テレビ等の娯楽的内容を提供できる。

(もっと読む)

映像処理装置及び映像処理方法

【課題】簡易な構成でインターレース映像信号をプログレッシブ映像信号に変換する際の画質の劣化を抑制することのできる技術を提供する。

【解決手段】本発明の映像処理装置は、補間画素の生成位置が斜め方向のエッジ部分か否かを判定し、且つ、補間画素の生成位置が斜め方向のエッジ部分である場合に該エッジの方向を判定する判定手段と、映像の動きがあり、且つ、前記判定手段で斜め方向のエッジ部分であると判定された補間画素の生成位置に対して、該エッジの方向に存在する画素を用いて補間画素を生成する生成手段と、を有し、判定手段は、補間画素の生成位置の1つ上または1つ下のラインの画素値が該補間画素の生成位置に垂直方向に隣接する位置で局所的に大きくまたは小さくなるか否かに基づいて、該生成位置が斜め方向のエッジ部分であるか否かを判定する。

(もっと読む)

映像処理装置

【課題】メモリを効率的に使用し、精度の高いフレーム検出と早い動きに対応したフレーム検出の両方を行うことができる映像処理装置を提供する。

【解決手段】映像処理装置100は、映像データが入力される処理選択部21、第1動き検索用メモリ部13、フレームメモリ部12、第2動き検索用メモリ部14、第2動き検索用メモリ部14へ画像フレームを供給するセレクタ部22、画像フレームのアドレス読み出し位置を制御するアドレス制御部20、第2動き検索用メモリ部14の画像フレームの対象画素の動きを検出する第1動き候補検出部15、第1動き検索用メモリ部13の画像フレームの対象画素の動きを検出する第2動き候補検出部16、対象画像の動き候補位置を第1動き検索用メモリ部13及び第2動き検索用メモリ部14に格納された画像フレームから検出する第3動き候補検出部17を備える。

(もっと読む)

71 - 80 / 1,468

[ Back to top ]