国際特許分類[H04Q3/00]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | 選択[1,2009.01] (7,489) | 選択配置 (1,125)

国際特許分類[H04Q3/00]の下位に属する分類

順列符号に応答するセレクタのための回路配置

径路指示数字の受信機のための回路配置 (2)

第1段の捜線切り換えのための回路配置

第二段またはその後段の捜線切り換えのための回路配置

共通回路,例.記録器制御器,マーカ,によって制御される間接選択のための回路配置 (308)

主交換機および従交換機または従局の間の接続を提供する配置 (780)

分配または出線 (4)

発呼加入者のクラスの識別

発呼加入者の番号の検出および表示 (2)

被呼加入者番号から出または入接続制御情報への翻訳 (2)

発呼または被呼加入者情報の一時的蓄積

国際特許分類[H04Q3/00]に分類される特許

21 - 27 / 27

UPCパラメータ設定機能を有するATM加入者回線収容装置

回線無瞬断切替方法および装置

【目的】 異なる伝送路を伝送する各データ信号の位相を正確に合わせた後各データ信号の切替えを無瞬断でできる。

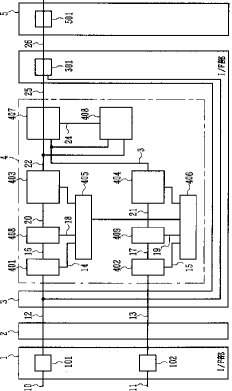

【構成】 SDH信号12、13が無瞬断切替部4に入力されると、無瞬断切替部4のJ1バイト識別部408でSDH信号16のパスIDにシンク側J1バイトが含まれているか否かが判定され、含まれているときエラスティックメモリ403に遅延量が設定される。一方、SDH信号13がJ1バイト同期照合部402にてJ1バイトの同期照合が実行されると、遅延量設定部405、406によりエラスティックメモリ403、404から読みだす遅延量の読出位相が同一となるように制御され、SDH信号22、23がデータ比較一致部408へ出力される。ここでSDH信号22、23の各ビットの一致が判定されると、無瞬断切替選択部407により、SDH信号22に代わりSDH信号23が選択されてインタフェース送信部5から送出される。

(もっと読む)

ATMインタフェースおよびシェーピング方法

【目的】VPI対応にセル送出間隔を制御すると共に、VCI毎のセル送出間隔を制御可能なシェーピング方法とATMインタフェースを提供する。

【構成】VPI毎に出力インタフェース速度を基準としたピークセル間隔を求め、VCI毎にVPIのピークセル間隔を基準とした時刻に従って相対的な送出時刻を計算した後、出力インタフェース速度を基準としたセル送出時刻を決定し、セルバッファよりセルを送出する。

【効果】複数のVPやVCが多重化された伝送路上で、VPI毎、VCI毎の申告トラヒックに従ったセル送出制御を行なうことができる。

(もっと読む)

ATM LANのコネクション確立および切断方法

【目的】 既存LANの上位プロトコルに依存することなく、ブリッジ本来のデータリンク層以下のプロトコルのみでコネクション確立に必要となる接続ATMアドレスを求めてコネクションの確立および切断を実現することを目的とする。

【構成】 既存のIEEE802準拠LANとATM LANとの間にブリッジA,Bを接続し、各ブリッジから同一サブネットに属する他のすべてのブリッジとPtoMPコネクションで接続し、各ブリッジはMACアドレスを記憶したテーブルを有している。既存LANからのパケットはブリッジAからブリッジBを介してPtoMPコネクションよりパケットを送信し、スループットが一定値以下であればマルチキャストを行ない、一定値を越えればPtoPコネクション設定してパケットを送信し、一定時間使用されなかった場合にはPtoPコネクションを切断する。

(もっと読む)

ATMネットワーク

【目的】 スループットの高いネットワークを構築する。

【構成】 ATMのノードをn行m列のマトリクス状に配置する。さらに、n行m列のノード間を伝送するセルの最長経路は各列毎にいずれか1個のノードを経由するように各ノードを接続する。

【効果】 ノード数が増加しても個々のノードが高いスループットを維持することができる。行列を宛先情報として用いるためルーティングが容易である。

(もっと読む)

再シーケンスシステム

【目的】 本発明は、第1のスイッチング・ノード (SN')とバッファレジスタ(OB)と第2のスイッチング・ノード(SN)との縦続接続を通るセル流のセルの再シーケンスにおける遅延ジッタを除去することを目的とする。

【構成】 再シーケンスシステムはさらにバッファレジスタ(OB)に関連してこのバッファレジスタ(OB)において各セルが受ける時間遅延を測定するように構成された遅延測定回路(DDM)を含み、セルが第2のスイッチング・ノード(SN)によって切換えられた後に、各セルの測定された遅延を再シーケンス手段(TSG、IC、REG、SUB、RSU)に伝達する手段が設けられ、このセルが受ける時間遅延が予め定められた一定の時間遅延値と伝達された遅延の間の差に等しいことを特徴とする。

(もっと読む)

非同期転送モードにおける中継線の動的帯域割当方式

21 - 27 / 27

[ Back to top ]