国際特許分類[H05K3/00]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路を製造するための装置または方法 (27,705)

国際特許分類[H05K3/00]の下位に属する分類

導電性物質が絶縁支持部材の表面に施されその後電流の伝導や遮へいのために使わない部分が表面から取り除かれるもの (964)

導電性物質が希望する導電模様を形成するように絶縁支持部材に施されるもの (3,771)

印刷回路の2次的処理 (3,717)

電気部品,例.抵抗器,を印刷回路に取り付けること (5,488)

印刷回路と他の印刷回路の組み合わせ (771)

絶縁基体と金属間の接着の改良 (829)

印刷回路への,または印刷回路間の電気的接続のための印刷要素の形成 (1,444)

絶縁された金属心回路の製造 (202)

多重層回路の製造 (6,503)

国際特許分類[H05K3/00]に分類される特許

1 - 10 / 4,016

プリント配線板の外形加工方法、及びプリント配線板

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

プリント基板組立体の配線設計方法及び製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

積層基板

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

実装構造体の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

感光性樹脂組成物、感光性エレメント、レジストパターンの形成方法及びプリント配線板の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

配線基板の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

穿孔用蓋板の製造方法

【課題】孔壁粗度を低減でき、コーティング層の表面の孔縮み、魚眼、接着性等の問題を解決した印刷回路基板材料である穿孔用蓋板の製造方法を提供する。

【解決手段】ジイソシアネート、ポリエステルジオール又はポリエーテルポリオール(I)、触媒及び溶剤を反応器で反応させ、そして、適量のジイソシアネート、ポリエーテルポリオール(II)、溶剤を添加して反応器で反応させ、そして、適量の鎖延長剤及びジイソシアネートを添加して反応させ続けて、最後に接着性のポリウレタン溶液を得るステップと、ポリウレタン溶液を高速撹拌しながら一定量の除イオン水を添加し、ポリウレタン分散液を調製し、均一に混合した後、静置して脱泡するステップと、ポリウレタン分散液をローラーコーティング又はコンマコーティングの方式により一定の厚みのアルミニウム箔の上表面に塗布し、乾燥、冷却して、穿孔用アルミニウム基蓋板製品を得るステップを含む製造方法。

(もっと読む)

焼結構造体の製造方法

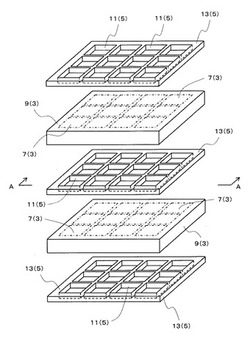

【課題】セラミック積層基板のような焼結構造体を製造する際に、生積層体を焼成する過程において、セラミックグリーンシートが15〜30%程度収縮するため、焼結構造体の寸法精度を高めることが難しいという課題があった。

【解決手段】本発明の一態様に係る焼結構造体の製造方法は、第1セラミック部材および第2セラミック部材を準備する準備工程と、第2セラミック部材の2次元配列された開口部が第1セラミック部材の2次元配列された基体領域と上下に重なり合うように、これらのセラミック部材を交互に積層して積層体を得る積層工程と、積層体を焼成一体化する焼成工程と、個片に分割する分割工程とを有しており、第1セラミック部材に含まれる第1焼結材料と同じ焼成条件における焼結収縮率が第1焼結材料よりも小さい第2焼結材料を第2セラミック部材が含んでいることを特徴としている。

(もっと読む)

感光性樹脂組成物、感光性エレメント、レジストパターンの形成方法及びプリント配線板の製造方法

【課題】感度及び解像度を十分に向上すると共に、テント信頼性にも十分に優れる感光性樹脂組成物、並びにこれを用いた感光性エレメント、レジストパターンの形成方法及びプリント配線板の製造方法を提供すること。

【解決手段】本発明の感光性樹脂組成物は、分散度が1.6以下のバインダーポリマーと、光重合性化合物と、アクリジニル基を1又は2有するアクリジン化合物を含む光重合開始剤とを含有する。

(もっと読む)

基板検査用治具の位置合わせ方法

【課題】簡便で且つ簡素に形成された基準基板を利用することによって行う基板検査治具の位置合わせ方法の提供。

【解決手段】検査対象となる基板の一方面に設定される複数の検査点と夫々導通接触する複数の第一接触部を有する第一基板検査用治具と、該基板の他方面に設定される複数の検査点と夫々導通接触する複数の第二接触部を有する第二基板検査用治具を備える基板検査装置において、第一接続手段5の第一接続部51と基準基板SWの一方の面に設定された第二基準部SW2に当接させた後、第二接続手段7の第二接続部71が基準基板SWの他方の面に設定された第一基準部SW1と当接するように位置合わせを行う。第二基準部SW2は、第二配線部SW5、孔部SW3と第一配線部SW4を介して第一基準部SW1と電気的に接続されているので、電源手段からの電気信号を判定手段が検出することで位置合わせを行うことができる。

(もっと読む)

1 - 10 / 4,016

[ Back to top ]