モサイド・テクノロジーズ・インコーポレイテッドにより出願された特許

1 - 8 / 8

ダイナミック連想メモリセル

【課題】2値または3値保存性能を有するダイナミック連想メモリを提供する。

【解決手段】ダイナミック連想メモリは、ビット・ラインとワード・ラインの交差部に位置する複数のダイナミック連想メモリセルを備える。各セルは、ワード・ラインに接続されるゲート端子およびビット・ラインに接続される第1ソース/ドレイン端子を有するアクセス・トランジスタと、アクセス・トランジスタの第2ソース/ドレイン端子に接続される第1プレートを有する第1メモリセル・キャパシタと、ポリシリコン相互接続層だけを介してアクセス・トランジスタの第2ソース/ドレイン端子に接続されるゲート端子を有する、マッチ・ラインの整合結果または不整合結果を示すための比較トランジスタとを含む。

(もっと読む)

モジュラーコンセント

【課題】コンセントを簡便かつ単純に、好ましくは専門家による設置の必要がなくアップグレードする方法やシステムを提供する。

【解決手段】コンセントは、ベースモジュール110aとインタフェースモジュール110bとを含む。ベースモジュール110aは、回線に接続し、建造物表面に取り付けられる。インタフェースモジュール110bは、データユニット接続を提供する。インタフェースモジュール110bは、ベースモジュール110aに機械的に取り付けられ電気的に接続する。回線によってさらに電話、電力、CATV等の基本サービス信号を搬送してもよい。

(もっと読む)

チャージポンプにおいて電流をクランプする回路

チャージポンプにおいて電流をクランプする回路が開示される。チャージポンプは、複数のスイッチング回路トランジスタを有するスイッチング回路を備える。同回路における第1及び第2の対のトランジスタの各々は、スイッチング回路トランジスタの内の対応する1つからの電流に対して、電流におけるスパイクが、同スイッチング回路トランジスタとチャージポンプのキャパシタとの間を通る経路を通って部分的にだけ伝送されるように、そのトランジスタがオフに切り替わっている間に追加経路を提供することができる。  (もっと読む)

(もっと読む)

適応データ圧縮のための方法および装置

【課題】適応データ圧縮を実行するための方法および装置を提供する。

【解決手段】未知の記号がエンコーダによりエンコードされるたびに、エンコーダは辞書に記号を加え、これをエンコードされたストリングで普通に伝送する。コードワードの前にある接頭語ビットの状態は、コードワードが、辞書に記憶される普通記号であるか、または記号もしくは記号のストリングのインデックスであるかを示す。コードワードが普通に記号を記憶する場合、デコーダは、先にデコードされた記号と現在デコードされた記号の第1の記号との連結により生じる一連の記号を加えることにより、かつ、この記号をその辞書に加えることにより、記号を学習する。コードワードがインデックスを記憶する場合、デコーダは、辞書において、それぞれのインデックスで、辞書に記憶される記号または一連の記号を抽出することにより、コードワードをデコードする。

(もっと読む)

共用メモリ配線を有する暗号化プロセッサ

【課題】さまざまな秘密鍵および公開鍵の暗号化アルゴリズムを処理するようプログラム可能な暗号化チップを提供する。

【解決手段】暗号化チップは、演算処理装置のパイプラインを含み、該演算処理装置の各々は、秘密鍵アルゴリズム内の1ラウンドを処理することが可能である。データは、該演算処理装置間で、デュアルポートメモリを介して転送される。中央処理装置は、単一サイクルのオペレーションで、グローバルメモリからの非常に幅の広いデータ語を処理することができる。加算器回路は、比較的小さい複数の加算器回路を使用することによって簡素化され、合計およびキャリが複数サイクルでループバックされる。乗算器回路は、非常に幅の広い中央処理乗算器となるよう連結することができるように、より小さい演算処理装置乗算器を適用することによって、複数の演算処理装置と中央処理装置との間で共用することができる。

(もっと読む)

スレーブQDRII準拠コプロセッサ

データを入力クロックから出力クロックに再同期させるための同期回路が提示される。第1の透過ラッチは、入力クロックに同期させたデータを受取る。第2の透過ラッチは、第1の透過ラッチからデータを受取り、出力クロックが挿入遅延だけ遅延させられたものである遅延出力クロックに依存してデータを出力する。出力ラッチは、第2の透過ラッチからデータを受取り、データを出力クロックに同期させる。  (もっと読む)

(もっと読む)

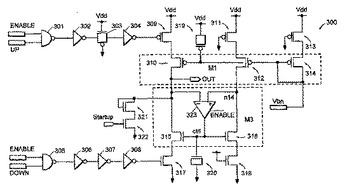

PLL/DLL用の高出力インピーダンスチャージポンプ

プルアップ回路とプルダウン回路と演算増幅器とを含む、位相ロックループ/遅延ロックループで使用するためのチャージポンプ。チャージポンプはプルアップおよびプルダウン回路の動作に関連したスタティック位相誤差を最小限にするように設計される。演算増幅器の使用はまた、低電源電圧の影響を軽減する。  (もっと読む)

(もっと読む)

遅延ロックループのための起動回路

遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]