ケイデンス デザイン システムズ インコーポレイテッドにより出願された特許

1 - 10 / 16

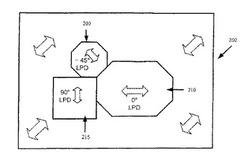

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

ダブルエッジトリガフリップフロップを有する回路用の一体型クロックゲーティングセル

ダブルエッジトリガ回路は、クロック信号及びイネーブル信号に応答してゲーテッドクロック信号を出力するクロックゲータと、ゲーテッドクロック信号に応答してデータ信号を送り出す第1のダブルエッジトリガフリップフロップと、クロック信号に応答してデータ信号を捕捉する第2のダブルエッジトリガフリップフロップとを含み、クロックゲータは、イネーブル信号が第1の論理状態のときに第1の論理値にてゲーテッドクロック信号を停止し、イネーブル信号が第2の論理状態のときに次のクロックエッジにてゲーテッドクロック信号を第1の論理値からスイッチングする。 (もっと読む)

電子回路デザインのさまざまな段階中にコンパクトな製造モデルを実行するための、機械によって実行される方法

【課題】電子回路デザインのさまざまな段階中にコンパクトな製造モデルを実行するための方法、システムおよびコンピュータプログラム製品を開示する。

【解決手段】いくつかの実施例では、上記方法またはシステムは、物理学ベースのデータを受取るまたは特定する。いくつかの実施例では、上記方法またはシステムは、高品質製造プロセスモデルを用いることによって、対応する製造プロセスのための物理学ベースのデータを受取るまたは特定する。いくつかの実施例では、上記方法またはシステムは、物理学ベースのデータを用いて、高品質製造プロセスモデルを微調整、修正または調整する。いくつかの実施例では、上記方法またはシステムは、適切なモジュールを呼出す。いくつかの実施例では、上記方法またはシステムは、コンパクトな製造モデルおよびコレクト・バイ・デザインモジュールを実行し、電子回路デザインのさまざまな段階に対して指針を提供する。

(もっと読む)

エミュレーションシステムを用いるデジタル設計のピーク電力検出

【課題】機能検証システムの使用に関する技術を提供する。

【解決手段】DUTの電力消費を解析する方法は、1以上の時間ウィンドウにDUT状態に関するエミュレーションデータを準備する段階、エミュレーションデータ及び1以上の時間ウィンドウの回路挙動を特徴付ける作動的モードの選択から作動的モード値を判断する段階、少なくとも1つの電力基準に基づいて各時間ウィンドウを1以上のセグメントに分割する段階、1以上のセグメントの電力活動値を判断する段階、電力活動値から1以上のセグメントの電力消費値を判断する段階、電力活動値及び電力消費値を用いて1以上のセグメントにわたる相対電力活動を判断し、1以上の時間ウィンドウの作動的モードにわたる高電力活動をターゲットにして1以上のセグメントを調節する段階、及びDUTの電力活動に関する1以上の値をコンピュータ可読媒体に保存する段階を含む。

(もっと読む)

相互接続の方法と装置

【課題】集積回路設計レイアウト用のルーティング方法。

【解決手段】レイアウトは、設計ネットリストとライブラリセルを備えることが出来る。マルチレベルグローバルルーティングは、各ネットにトポロジカルワイヤを生成することが出来る。設計には、領域志向グラフベースのディテールルーティングを実行することが出来る。ディテールルーティング後のルーティング最適化を実施し、更にルーティング品質を改善することが出来る。幾つかの方法は、いつも又はある時シングルスレッドでも良く、及び/又はある時又はいつもマルチスレッドでも良い。

(もっと読む)

組込形ソフトウェアの実行時間の統計的評価のための方法及び装置

【課題】ソフトウェアの実行時間を推定する推定装置を提供する。

【解決手段】ソフトウェアの実行時間を統計的に推定する推定方法は、ベンチマークプログラムのセットに基づいて、ターゲットプロセッサのモデルを準備するステップと、推定されるソフトウェアとベンチマークプログラムとを相関させるステップと、相関されたソフトウェアをモデルに適用し、ソフトウェアの実行時間の推定値を判定するステップとを有する。このモデルは、ベンチマークプログラムの実際の実行時間を判定し、ベンチマークプログラム内の仮想命令の数を判定し、仮想命令と実際の実行時間とを相関させる予測式を決定することにより開発される。予測式は、仮想命令の相関分析を行い、高度に相関する命令を除外し、逐次線形重回帰分析と線形重回帰分析とを組み合わせて実行することによって決定される。

(もっと読む)

合成検証のための自動仮定を生成する方法、システム、及びコンピュータプログラム製品

【課題】2つの言語を分離する最小決定論的有限オートマトンを計算する方法、システム、及びコンピュータプログラム製品を提供する。

【解決手段】仮定−保証推論における中間アサーションとして作用する厳密な最小オートマトンを計算する方法、システム、及びコンピュータプログラム製品。一実施形態では、厳密な最小オートマトンの計算は、サンプリング手法及びブール充足可能性を用いて実行される。本明細書で説明する方法は、形式的検証のツールの一部として使用することができる。

(もっと読む)

ハードウエアエミュレーションシステムのプロセッサを同期化する方法及び装置

プロセッサベースのハードウエアエミュレーションエンジン、特に、エミュレーションエンジン内でプロセッサを同期化する方法及び装置を提供する。同期したプロセッサを使用してハードウエアエミュレーションを実施する方法、装置、及びそのためのハードウエア設計をコンパイルする方法を説明する。装置は、ハードウエア設計に関するデータを評価するためのプロセッサ群を形成する複数のプロセッサと、ハードウエア設計の少なくとも一部分をエミュレートしている間にプロセッサ群の演算を同期させるためのシンクロナイザとを含む。方法は、ハードウエア設計に関するデータを評価するためのプロセッサ群を形成する複数のプロセッサに同期信号を供給する段階と、プロセッサ群から待機信号を受信する段階と、プロセッサ群に実行信号を供給する段階とを含み、実行信号により、プロセッサ群は、サブモデルを評価する。ハードウエア設計をコンパイルする方法は、少なくとも1つの高レベル構成概念を演算のシーケンスに変換する段階と、少なくとも1つの条件付きサブモデルを構成する演算のシーケンスを特定する段階とを含む。 (もっと読む)

プロセッサの異種クラスターを有するハードウエアエミュレーションシステム

【課題】異種プロセッサベースのハードウエアエミュレーションシステムを提供する。

【解決手段】プロセッサの異種クラスターを有するハードウエアエミュレーションシステム。ハードウエアデザインをエミュレートするための装置は、複数のプロセッサを含み、各プロセッサは、エミュレーションサイクル中に異なる機能を実行する。この装置によって実行される方法は、データフェッチプロセッサを使用してデータアレイからデータを検索する段階、検索したデータをデータフェッチプロセッサを使用して評価し、出力ビットを生成する段階、出力ビットをクラスター内クロスバーに供給する段階、及びデータ記憶プロセッサを使用して出力ビットをデータアレイに記憶する段階を含む。

(もっと読む)

可変入力プリミティブを有するハードウェアエミュレータ

第1の入力幅を有する関数を評価するための第1のプリミティブと、第1のプリミティブに結合された第2のプリミティブであって、第2の入力幅を有する関数を評価するための第2のプリミティブと、を有し、第1の入力幅が第2の入力幅に等しくないハードウェアエミュレータである。第1のプリミティブ又は第2のプリミティブの何れかの一方の使用は、評価される関数に応じて選択される。 (もっと読む)

1 - 10 / 16

[ Back to top ]