テキサス インスツルメンツ インコーポレイテッドにより出願された特許

1 - 10 / 19

無線通信システムにおいて基準信号を割り当てるための方法及び装置

無線通信システムにおいて基準信号を割り当てるための方法及び装置を開示する。開示する例示的な装置は、無線領域に割り当てられたパラメータに基づいて基準シーケンス(505)を生成するための基準信号生成器(501)を含み、この場合、パラメータは、無線領域の第1の装置によって第1の時間中に送信される第1の基準シーケンスを指定し、第1の基準シーケンスは、第1の無線領域に隣接する第2の無線領域の第2の装置に割り当てられる第2の基準シーケンスとは異なる。基準シーケンス生成器は、パラメータに基づいて第1の時間のための巡回シフトを選択するための巡回シフトセレクタ(503)と、選択した巡回シフトに基づいて第1の基準信号を巡回シフトするための巡回シフタ(506)とを含む。例示的な装置は、巡回シフトされた第1の基準シーケンスを送信するための送信アダプタ(510)をさらに含む。 (もっと読む)

改善されたコンタクトヒューズを備えた半導体デバイス

本発明の1つの態様は、集積回路(IC)(400b)を提供する。ICは、トランジスタ(410b)及びコンタクトヒューズ(422b)を含む。コンタクトヒューズは各々導電層(424b)を含み、錐体形コンタクト(426b)は、導電層に接触する狭い端部と、導電層上に配置される第1の金属層(427b)とを有する。錐体形コンタクトの広い端部は第1の金属層に接触する。錐体形コンタクトは、約1.2以上である、狭い端部に対する広い端部の開口の比を有する。コンタクトヒューズは各々、第1の金属層上に配置されて接触するヒートシンク(432b)を更に含む。 (もっと読む)

駆動回路及び該駆動回路で使用されるドレイン拡張型トランジスタ

トランジスタ(100)は、第1の導電型であり第1の半導体領域と電気的に接続するソース領域を備える。また、トランジスタは、第1の導電型であり第1の半導体領域とは異なる第2の半導体領域と電気的に接続するドレイン領域を備える。第1の半導体領域と第2の半導体領域との間に境界面が存在する。トランジスタは、ドレイン領域(108)よりも境界面に近接した位置に配置される少なくとも一部分を含む電圧タップ領域を備える。また、混合技術回路が開示されている。  (もっと読む)

(もっと読む)

完全な差動ボイスコイルモータ制御のための、オンチップ補償

差動ボイスコイルモータ制御機能を備えるディスクドライブコントローラが開示される。差動ボイスコイルモータ制御機能は、内部制御ループのための、直列接続された1以上のMOSトランジスタから成る抵抗器を含む、オンチップ補償ネットワークを備える。補償ネットワークにおけるMOSトランジスタのゲートは、調整電流に基づいてバイアス電圧で駆動される。調整電流は、集積回路における過程及び温度変化、例えばオンチップコンデンサ内の変化などに伴って変化するよう、得られる。オンチップ補償ネットワークは、内部制御ループを適切に補償するよう、ディスクドライブ内のボイスコイルモータの駆動において所望の周波数応答を与えるよう、十分正確に調整可能である。 (もっと読む)

非線形支持を有するアナログMEMS

開示される実施形態は、非線形抵抗を与える1つ以上の梁によって支持される枢動マイクロミラー(102)を備えるアナログMEMSデバイスを示す。梁(120)が撓みに対して抵抗を与えるのに対して、電極(105)はマイクロミラーを静電的に引き付けることができる。力が等しいとき、マイクロミラーは目標角で保持される。実施形態で開示される梁支持材は、静電力の非線形性状により良く合致する非線形支持をマイクロミラーに与えるので、それは従来のねじりヒンジ支持材(150)よりも優れている。 (もっと読む)

HVMOSデバイスの性能向上方法

【課題】本方法は、異なるチャンネル長さ及び実質的に同じ閾値電圧を有するDEMOSデバイスを製造するものである。

【解決手段】第1及び第2のデバイスについて閾値電圧が選択される。第1及び第2のウェル領域(204)が形成される。第1及び第2のドレイン拡張領域(206)は、ウェル領域内に形成される。第1及び第2のバックゲート(208)領域が、選択された閾値電圧に従ってウェル領域内に形成される。第1及び第2のゲート構造が、異なるチャンネル長さを有する第1及び第2のウェル領域の上に形成される。第1のソース領域(212)が、第1のバックゲート領域内に形成され、第1のドレイン領域が第1のドレイン拡張領域内に形成される。第2のソース領域(212)が第2のバックゲート領域内に形成され、第2のドレイン領域が第2のドレイン拡張領域内に形成される。

(もっと読む)

半導体デバイスの耐湿信頼性を改良しはんだ付け性を高めたリードフレーム

半導体デバイスは卑金属で形成された構造(105)を有するリードフレームを有し、上記構造はチップマウントパッド(302)及び複数のリードセグメント(303)からなる。上記卑金属をカバーしているのは、順番に、上記卑金属上の連続ニッケル層(201)、上記ニッケル上のパラジウムの層であり、上記構造のチップ側上のパラジウムの層(203)は上記チップの反対側のパラジウムの層(202)より厚く、更に、上記チップの反対側の上記パラジウムの層(202)上には金の層(204)が存在する。半導体チップ(310)はチップマウントパッドに取付けられ、導電性接続(312)が上記チップと上記リードセグメントとを接続している。ポリマーカプセルコンパウンド(320)が上記チップ、上記接続、及び上記リードセグメントの部分をカバーしているが、外部部品にはんだリフロー取付けするために利用可能な他のセグメント部分はカバーしない。  (もっと読む)

(もっと読む)

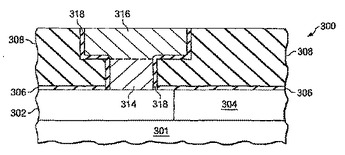

細孔シーリングライナーのデュアルダマシン方法及びデバイスへの統合

デバイスは、細孔シーリングライナーを有するダマシン層を使用し、半導体ボディを含んでいる。金属相互接続(302)からなる金属相互接続層が、半導体ボディ上に形成される。誘電層(308)が、金属相互接続層上に形成される。導電性トレンチフィーチャ(316)及び導電性バイアフィーチャ(314)が、誘電層内に形成される。細孔シーリングライナー(318)が、導電性バイアフィーチャの側壁に沿ってのみ、及び導電性トレンチフィーチャの側壁及び底面に沿って形成される。細孔シーリングライナーは、導電性バイアフィーチャの底面に沿っては実質的に存在しない。  (もっと読む)

(もっと読む)

歪みシリコンにおける欠陥低減のための窒素ベース注入物

トランジスタ(200)が半導体基板(202)上に作製され、ここで基板の降伏強さ又は弾性が向上され、又は他の方法で適合される。歪み誘起層(236)がトランジスタを覆って形成され、これに歪みを加えてトランジスタの動作特性を変更し、より詳細にはトランジスタ内のキャリアの移動度を向上させる。キャリア移動度を向上させることにより、トランジスタの大きさを低減させることが可能となると同時に、トランジスタを所望通りに動作させることが可能となる。しかしながら、トランジスタの作製に伴う高い歪み及び温度は、有害な塑性変形をもたらす結果となる。従って、窒素を基板に、より詳細にはトランジスタのソース/ドレイン延長領域(220,222)及び/又はソース/ドレイン領域(228,230)に導入することによって、シリコン基板の降伏強さが適合される。窒素は、ソース/ドレイン延長領域形成及び/又はソース/ドレイン領域形成の一部として窒素を付加することにより、トランジスタ作製中に容易に導入することができる。基板の降伏強さが向上すると、歪み誘起層に起因するトランジスタの塑性変形が軽減される。 (もっと読む)

ダイオードクランプを有するドレイン拡張されたMOSFETS

上側の拡張されたドレインMOSドライバ・トランジスタ(T2)が提供される。このトランジスタ内では、拡張されたドレイン(108、156)が、第2の埋められた層(130)によって第1の埋められた層(120)から分離される。なお、内部又は外部のダイオード(148)が、第1の埋められた層(120)と拡張されたドレイン(108、156)の間にカップルされて、降伏電圧を増大させる。 (もっと読む)

1 - 10 / 19

[ Back to top ]