セムテック コーポレイションにより出願された特許

1 - 4 / 4

抵抗性デジタル/アナログ変換

【課題】抵抗性構成要素を利用するデジタル/アナログ変換の技術及び方法を提供する。

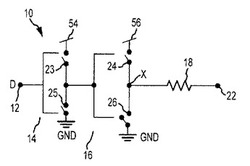

【解決手段】RDAC回路は、nビットデジタル入力信号から導出されたアナログ出力信号を供給する。RDAC回路は、複数の抵抗性回路分岐10を含み、各抵抗性回路分岐は、プルアップ/プルダウンネットワーク構成に配置する。RDAC回路は、並列に位置決めされた複数の抵抗性回路分岐を含み、複数の抵抗性回路分岐の各々は、第1のインバータ回路14、第2のインバータ回路16、及び抵抗性構成要素18を含む。RDAC回路は、アナログ出力信号を供給する出力ノードを含む。

(もっと読む)

逐次近似アナログ・デジタル変換

【課題】アナログ入力信号をデジタル出力信号に変換するためのシステム及び方法を提供する。

【解決手段】システムは、DAC電流を供給するための電流モード(CM)デジタル・アナログ変換器(DAC)回路210を含む。比較器回路250は、DAC電流及びアナログ入力信号に基づいて決定されたエラー信号に応答して比較器信号を発生する。逐次近似レジスタ回路270は、比較器信号に応答して、DACコード信号274又はデジタル出力信号272のうちの少なくとも1つを発生する。DACコード信号をCM DAC回路によって用いて、DAC電流を制御する。

(もっと読む)

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

高速シリアライザ、関連部品、システム、及び方法

通信システムは、データチャンネルの第1セットを第1データチャンネルに多重化すると共にデータチャンネルの第2セットを第2データチャンネルに多重化するように構成されたマルチプレクサと、ディレイアジャストコマンドに基づいて前記第1データチャンネルの遅延を調節するように構成されたディレイアジャスタと、を含む。この通信システムは、前記遅延後の第1データチャンネルを第1出力データチャンネルへ増幅するように構成された第1アンプと、前記第2データチャンネルを第2出力データチャンネルへ増幅するように構成された第2アンプと、を含む。さらに、当該通信システムは、前記第1出力データチャンネルを、光モジュレータを駆動するための第1駆動信号に変換するように構成された第1ドライバと、前記第2出力データチャンネルを、前記光モジュレータを駆動するための第2駆動信号に変換するように構成された第2ドライバと、を含む。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]