キロパス テクノロジー インコーポレイテッドにより出願された特許

1 - 3 / 3

超薄膜誘電体のブレークダウン現象を利用した半導体メモリセルセル及びメモリアレイ

【課題】 超薄膜誘電体のブレークダウン現象を利用した半導体メモリセルセル及びメモリアレイを提供する。

【解決手段】 超薄膜誘電体(312)の周りに構成されるデータ記憶素子(115)を有する半導体メモリセル(300)を使用し、超薄膜誘電体(312)にストレスを与えてブレークダウン(ソフトまたはハードブレークダウン)させてメモリセル(300)のリーク電流レベルを設定することにより情報を記憶する。セル(300)が引き込む電流を検知することによりメモリセル(300)からの読出しが行なわれる。適切と考えられる超薄膜誘電体(312)は約50オングストローム以下の厚さの高信頼度のゲート酸化膜である。

(もっと読む)

電気的にプログラム可能なヒューズ・ビット

データ内容を読み出すために復号またはアドレス指定する必要がないワンタイム・プログラマブル(OTP)不揮発性ヒューズ・メモリ・セル。各ヒューズ・メモリ・セルは、その出力のところにラッチされ、その内容をいつでも使用することができる。 例えば、コード格納メモリ、直列構成メモリ用に、またID(識別)、トリミング、および他の製造後のシステム・オン・チップ(SoC)カスタム化ニーズのための個々のヒューズ・ビットとして使用することができる。一時的にデータを格納し、設計を試験するための手段も含む。他の実施形態の場合には、1つのメモリ・セルで2つの差動的にプログラムしたヒューズを使用して、選択およびプログラミング回路がマージされる。  (もっと読む)

(もっと読む)

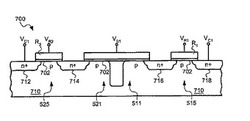

単一トランジスタを用いる高密度半導体メモリ・セル及びメモリ・アレイ

列ビット線と行ワード線の交差点に配置されたトランジスタで構成されるプログラム可能なメモリ・セルを開示する。トランジスタは、列ビット線から形成されるゲート及び行ワード線に接続されたソースを有する。列ビット線と行ワード線との間に電位差を印加してトランジスタのゲートの下にある基板内にプログラムされたn+領域を作ることによってメモリ・セルをプログラムする。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]