インテルユニバルシテール、ミクロエレクトロニカ、セントラム、フェーゼットウェーにより出願された特許

1 - 9 / 9

サーマルバジェットを低減する接合およびケイ化物の形成

半導体基板(1)の上に金属ケイ化物層(12,13,14,18,19)を形成する方法であって、半導体基板(1)は少なくともドーパント領域(5)を含み;ドーパント領域(5)は極浅接合領域を含み;同方法は第1のステップとしてドーパント領域(5)を形成する少なくとも1つの不純物注入処理(IB dopant)を含み;同方法は第2のステップとしてドーパント領域(5)の上に金属ケイ化物層(12,13,18,19)を形成する少なくとも1つの金属注入処理(IB metal)を含み、さらに同方法は第1および第2のステップより後に実行される第3のステップとしてドーパント領域(5)を活性化し同時に金属ケイ化物層(12,13,14,18,19)を形成する低温アニール処理を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

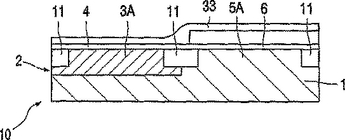

この発明は、基板(1)と半導体本体(2)とを有する半導体装置(10)であって、第一のチャネル領域(3A)と第一の導体を含み且つ誘電体層(4)によりチャネル領域から分離された第一のゲート電極(3B)とを有する第一の(NMOS)FET(3)を備え、そして、第二のチャネル領域(5A)と第一の導体とは異なる第二の導体を含み且つ誘電体層(4)によりチャネル領域(5A)から分離された第二のゲート電極(5B)とを有する第二の(PMOS)FET(5)を備え、第一及び第二のゲート電極(3B、5B)を形成するために、誘電体層(4)が備えられた半導体本体(2)上に第一の導体層(33)が堆積され、導体層(33)は、その後、第一のチャネル領域(3A)外部で除去され、その後、第二の導体層(55)が半導体本体(2)上に堆積され、そして、第一の導体層(33)が堆積される前に、誘電体層(4)上に中間層(6)が堆積される半導体装置の製造方法に関する。この発明によれば、中間層(6)のための材料として誘電体層(4)に対し選択的にエッチング可能な材料が選ばれ、そして、第一の導体層(33)が堆積される前に、第一のチャネル領域(3A)の位置で中間層(6)が除去され、そして、第一の導体層(33)が堆積され、第一のチャネル領域(3A)外部で除去された後に、そして、第二の導体層(55)が堆積される前に、第二のチャネル領域(5A)の位置で中間層(6)が除去される。従って、FETが、簡単な方法で、且つ、それらのゲート誘電体にダメージを与えずに得られる。好ましくは、中間層(6)に対して選択的にエッチング可能なさらなる中間層(8)が中間層(6)上に堆積される。  (もっと読む)

(もっと読む)

互いに重ねて堆積させた金属層の積層体中に形成されたゲート電極を含むMOSトランジスタを備える半導体デバイスの製造方法

互いに重ねて堆積させたいくつかの金属層(8,9,13;8,12,13)として形成したゲート電極(15,16)を有するMOSトランジスタを備える半導体デバイスの製造方法。この方法では、シリコン本体(1)に、ゲート誘電体層(7)を備えるシリコン活性領域(4,5)およびこれらの領域を互いに絶縁するフィールド分離領域(6)を形成する。次いで、第1の金属層(8)を堆積させ、活性領域(4)の一部の位置でその層中に局所的に窒素を導入する。次いで、第1の金属層上に第2の金属層(13)を堆積させ、その後それらの金属層中にゲート電極をエッチングする。第1の金属層中に窒素を導入する前に、第1の金属層上に窒素透過性の第3の金属補助層(9)を堆積させる。したがって、その下にあるゲート電極に損傷を与える危険なく、第1の金属層を窒化することができる。金属の仕事関数を実質的に変えることが可能であるとともに、NMOSおよびPMOSを備える半導体デバイスが実現される。  (もっと読む)

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、半導体本体(1)と基板(2)とを備えた半導体装置(10)であって、少なくとも一つの半導体素子(3)を備え、そして、少なくとも一つの接続領域(4)と、接続領域(4)に接続された上部に横たわる帯状接続導体(5)とが設けられ、帯状接続導体と接続領域とが共に誘電体材料内に窪んでおり、続いて、第一の誘電体層(6)と、第一のハードマスク層(7)と、そして、第二の誘電体層(8)とが半導体本体(1)上に堆積され、接続領域(4)が形成される部位において、炭素とフッ素との化合物を含むプラズマを用いたプラズマエッチングにより第一の誘電体層(6)内にバイア(44)が形成され、そして、この構造の上部に堆積されたパターンニングされたフォトレジスト層が存在している状態で、接続導体(6)が形成される部位において、プラズマエッチングにより第二の誘電体層(8)内にトレンチ(55)が形成され、接続領域(4)と接続導体(5)とをそれぞれ形成するために、バイア(44)及びトレンチ(55)が導電材料で満たされ、そして、トレンチ(55)が形成される前に、既に形成されたバイア(44)が有機材料(2)で満たされる半導体装置の製造方法に関する。この発明では、バイア(44)のエッチング中にバイア(44)が同時にほぼ完全に有機材料(20)で満たされるように、第一の誘電体層(6)の材料と、プラズマエッチングによる第一の誘電体層(6)内のバイア(44)の形成中のエッチング条件とが選ばれ、この構造及びプラズマ内に既に存在する有機材料から有機材料(20)が形成される。エッチングの間にレジスト層が存在することと、そこで炭素とフッ素との化合物を用いること以外に、関わる条件は、第一(そして第二)の誘電体層(6,8)とこれら層(6,8)のエッチングの間の電力の選択に関する。  (もっと読む)

(もっと読む)

半導体装置の製造方法並びにそのような方法で得られる半導体装置

この発明は、半導体材料の半導体本体(1)が設けられ、該半導体本体表面にソース領域(2)及びドレイン領域(3)を有し、ソース領域(2)とドレイン領域(3)との間にゲート領域(4)を有し、ゲート領域(4)は、ゲート誘電体(5)によって半導体本体(1)の表面から分離されているさらなる半導体材料の半導体領域(4A)を備え、ゲート領域(4)近傍にソース領域(2)とドレイン領域(3)とを形成する複数のスペーサ(6)を有し、ソース領域(2)とドレイン領域(3)とに金属と半導体材料との化合物(8)を形成するための金属層(7)が設けられ、そして、ドレイン領域(3)に金属と上記さらなる半導体材料との化合物(8)を形成するためのさらなる金属層(7)が設けられる電界効果型トランジスタを有する半導体装置の製造方法に関する。ソース、ドレイン、ゲート領域(2,3,4)をシリサイド化するのに異なる金属層が用いられる既知の方法は様々な欠点がある。本発明の方法は、複数のスペーサ(8)が形成される前に、半導体領域(4A)に対して選択的にエッチングされうる材料の犠牲領域(4B)が半導体領域(4A)の上部に堆積され、複数のスペーサ(6)が形成された後に、エッチングにより犠牲領域(4B)が除去され、犠牲領域(4B)が除去された後に、ソース、ドレイン、ゲート領域(2,3,4)を含む単一の金属層(7)が堆積されることを特徴する。この方法では、一方で、単一の金属層のみと小数の容易な工程とが必要で、そして、現存する(シリコン)技術と適合し、他方で、完全にシリサイド化されたゲート(4)において空乏層の影響を受けない(MOS)FETが得られる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

半導体装置の製造方法において、半導体本体(1)の表面(3)の単結晶シリコン領域(4)直近に位置するシリコン酸化物領域(5)内に非単結晶補助層(8)が形成される。補助層は二工程で形成される。第一の工程において、ガス状砒素化合物を有する雰囲気内で半導体本体が加熱され、第二の工程において、そのガス状砒素化合物の代わりにガス状シリコン化合物を有する雰囲気内で半導体本体が加熱される。従って、シリコン酸化物領域に、自己整合的に、アモルファス又は多結晶シリコンの種層が設けられる。  (もっと読む)

(もっと読む)

エピタキシャル層を形成する方法および装置

本発明は、シリコン基材上にIV族元素をベースとするエピタキシャル層を化学蒸着により堆積させる方法であって、キャリヤーガスとして窒素または希ガスの一種を使用する、方法を提供する。本発明はさらに、ガス入口(14)およびガス出口(16)を有するチャンバー(12)と、チャンバー(12)の中にシリコン基材を取り付ける手段(18)とを備えてなる化学蒸着装置(10)を提供するが、該装置は、入口に接続され、なおかつキャリヤーガスとして窒素または希ガスを供給するように配置されたガス供給源を包含する。  (もっと読む)

(もっと読む)

分離材料で満たされた溝より成るフィールド分離領域を有する半導体装置の製造方法

活性領域(3)を取り囲むフィールド分離領域(2)が設けられた表面(4)を有するシリコン本体(1)を備えた半導体装置の製造方法。この方法では、シリコン本体の表面に、ある材料の補助層(5)が設けられ、その上に、酸化処理の間に、シリコン本体のシリコン上よりも厚くシリコン酸化物の層が形成される。ここでは、シリコン及びゲルマニウムを備える補助層が上記表面上に形成され、そして、前記補助層はSixGe1−x−yCy、ここでは、0.70<x<0.95そしてy<0.05の層であると好ましい。次に、フィールド分離領域が形成される位置において、補助層内に開口(9)が形成され、そして、シリコン本体内にトレンチ(11)が形成される。次に、トレンチの壁(12)上にシリコン酸化物層(13)が設けられ、そして、開口の壁(10)にシリコン窒化物層(14)が設けられ、両者とも酸化処理により形成される。補助層はその厚み全体に渡っては酸化されない。酸化処理の後、分離材料の層(18)が堆積され、これがトレンチ及び開口を完全に満たす。続いて、補助層(17)の非酸化部分が露出するまで平坦化処理が行われ、そして、補助層の露出部分が除去される。従って、活性領域(3)上に延在する端部(19)を有するフィールド分離領域(2)が形成される。  (もっと読む)

(もっと読む)

リソグラフィ投影装置、電子デバイスを製造するための方法及び基板、及び得られる電子デバイス

本発明は、基板又はウエーハ上にパターンを形成するためのウエーハステッパ等のリソグラフィ投影装置を提案するものであり、当該リソグラフィ投影装置は、(化学)放射線源又は光源(2)と、前記光源から発した光を、マスク(6)上に導くための照射光学系(4)と、前記マスクからの回折放射線又は回折光を、結像される前記基板/ウエーハに導くための投影光学系(8)とを備え、光学フィルタ(9)が、前記投影光学系の下流側に設けられ、結像可能な基板(7)が、結像される面に光学フィルタ(9)を有する。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]