プロモス テクノロジーズ ピーティーイー リミテッドにより出願された特許

1 - 3 / 3

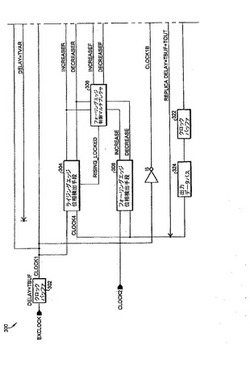

DDRメモリデバイスのデータ出力のデューティサイクル制御及び正確な調整のための複数の電圧制御された遅延ラインの利用

【課題】DDRメモリにおいて、デューティの歪みを生じさせることなくデータ信号のライジングとフォーリングエッジの双方を効果的に同期させるDLL回路を提供する。

【解決手段】DDRメモリの出力データ信号の50%のデューティを保証するための3DLL回路であって、第1クロック信号から第2クロック信号を生成する第1DLLと、前記DDRの出力データ信号の1つの遷移を調整する第2DLLと、前記DDRの出力データ信号の第2の遷移を調整する第3DLLを備え、前記第2、第3DLLに設けられた第2、第3遅延ラインの出力のライジングエッジにより生成されるライジングとフォーリングエッジを有し、前記DDRの出力データ信号をイネーブルにする第3クロック信号と、前記第3クロック信号を固定時間遅延させ、前記第2、第3DLLの第2、第3位相検出手段へフィードバックすることにより生成される第4クロック信号とを有する構成とする。

(もっと読む)

集積回路用の高速かつ低電力の入力バッファ

【課題】集積回路向けの高速かつ低電力入力バッファを提供する。

【解決手段】本発明の集積回路向けの高速かつ低電力入力バッファでは、入力電圧VINがプルアップトランジスタとプルダウントランジスタの両方に結合されている。特定の実施の形態によれば、入力バッファは、動作のキャリブレーションフェーズであって、アクティブな動作モードではない間に基準電圧入力VREFを利用する。スルー電流の最大レベルは、VIN=VREFであるときに供給され、より低いレベルのスルー電流は全ての他のVIN電圧で供給される。開示されるような入力バッファを組み込んだ集積回路装置では、デバイスの入力ピン当たり2つの(又は2つを超える)の入力バッファが利用される場合がある。

(もっと読む)

集積回路用の高速かつ低電力の入力バッファ

【課題】 集積回路向けの高速かつ低電力入力バッファを提供する。

【解決手段】 本発明の集積回路向けの高速かつ低電力入力バッファでは、入力電圧VINがプルアップトランジスタとプルダウントランジスタの両方に結合されている。特定の実施の形態によれば、入力バッファは、動作のキャリブレーションフェーズであって、アクティブな動作モードでない間に基準電圧入力VREFを利用する。スルー電流の最大レベルは、VIN=VREFであるときに供給され、より低いレベルのスルー電流は全ての他のVIN電圧で供給される。開示されるような入力バッファを組み込んだ集積回路装置では、デバイスの入力ピン当たり2つ(又は2を超える)の入力バッファが利用される場合がある。

(もっと読む)

1 - 3 / 3

[ Back to top ]