インテグレイテッド・デヴァイス・テクノロジー,インコーポレイテッドにより出願された特許

1 - 2 / 2

パケット処理スイッチおよびそれを動作させる方法

パケットスイッチング集積回路チップは、パケット、例えば、RapidIO(商標)に準拠したパケットを複数の外部ソースから受信し、受信パケット内のデータを複数の外部受信装置に選択的に転送するように構成される。チップは、第1の受信パケットを変更することなく転送し、かつ、第2の受信パケットを終結し、それのペイロードを前処理し、新しいパケットを生成するように構成される。チップは、ビット拡張、ビット切り捨て、ビット並べ替え、および/または、ビット算術演算のような信号サンプル処理操作を、第2の受信パケットに施すように構成することができる。さらにチップは、受信パケット内の宛先アドレスに基づいて、第1および第2の受信パケットを管理するように構成することができる。  (もっと読む)

(もっと読む)

小さいフットプリントおよび効率的なレイアウトアスペクト比を有するターナリ検索機能付きメモリ(TCAM)セル

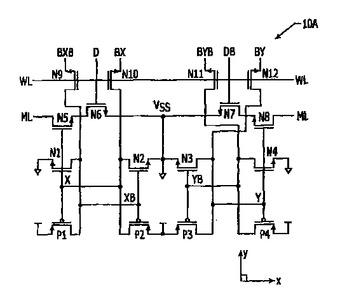

スケーラビリティを高める効率的なレイアウトアスペクト比および極めて小さいレイアウトフットプリントサイズを有するターナリCAMセルが提供される。また、セルは、ビット線、データ線、マッチ線に対する高い歩留りの相互接続を容易にする高度の対称性も有している。16TターナリCAMセルは、セルの第1の側に隣接して延びる第1および第2の対のアクセストランジスタと、セルの第2の側に隣接して延びる第1および第2の対の交差結合インバータとを有している。また、4T比較回路の第1及び第2の半分部位も設けられている。4T比較回路の第1の半分部位は、第1の対のアクセストランジスタと第1の対の交差結合インバータとの間で延びるように位置されている。同様に、4T比較回路の第2の半分部位は、第2の対のアクセストランジスタと第2の対の交差結合インバータとの間で延びるように位置されている。

(もっと読む)

(もっと読む)

1 - 2 / 2

[ Back to top ]