パナビジョン イメージング リミテッド ライアビリティ カンパニーにより出願された特許

1 - 4 / 4

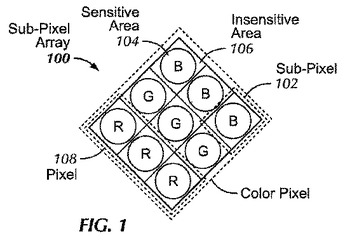

カラー部分画素アレイの解像度を増大すること

デジタル画像の解像度を増大することは、斜めに配置されたカラー部分画素アレイを用いて画素をサンプリングしかつサンプリングされた画素データから欠落した画素を生成することにより開示される。第1の方法は、デジタルカラー撮像画素をそれぞれ他の直交の表示画素へマッピングすることである。欠落した表示画素は、隣接するカラー撮像画素からデータを補間しかつ隣の表示画素からカラー情報を平均化することにより計算される。この平均化することは、均等に周辺画素に重み付けをし、又は強度情報に基づき周辺画素に重みを与えることにより行われ得る。第2の方法は、補間の代わりに計算したカラー撮像部分画素データを利用することである。直交表示のための欠落したカラー画素は、画素のロウカラー画素間において形成された部分画素アレイから直接的に得ることができる。  (もっと読む)

(もっと読む)

可変アクティブ画像領域イメージセンサ

本発明の実施態様は、可変アクティブ画像領域を提供する。部分画素は可変選択グループ内に配置され、画素グループを備える。画素グループの部分画素は、複数の選択部分画素グループに属することができる。セレクタは、可変部分画素選択を提供するために、1つ又は複数の選択部分グループの組み合わせ選択するように構成される。可変部分画素選択は、可変アクティブ画像領域の異なる側面(例えば、位置、サイズ、形状)を変化させることができる。これらの側面を変化させることは、アライメント及び較正の観点で、大きな柔軟性につなげることができる。全ての部分画素うちのいくつかだけを選択することは、少ない処理及び低い電力消費量につなげることができる。複数の部分画素値は、1つの画素グループ値内で処理されることができる。異なる可変選択グループのための可変部分画素選択は独立とされることができる。  (もっと読む)

(もっと読む)

食い違い画素を有する複数チップを使用する走査型イメージャ

ソリッドステート・イメージング・システムは、1つの画素連続の画素が、他の画素連続の画素に関してずらされ、即ち食い違いにされている第1および第2の画素連続を有する少なくとも1つのCMOSイメージャを有する。複数のイメージャが端から端へと配列され、ジャンパ線が画素出力導体または各々を接続し、それによって画素は各々の画素連続の共通出力増幅器へ入り、チップ間オフセット電圧を最小にする。画素は相互から斜めにずらされ、カラー・リボンフィルタがイメージ区域を斜めに横切って配列されるカラー・イメージャを構築することができる。この配列はカラーのクロストークを最小にする。

(もっと読む)

(もっと読む)

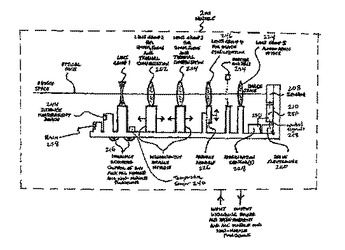

レンズ制御方法および装置ならびに、これを組み込んだカメラモジュール

合焦または物体距離、ズーム、、温度補償および安定化のうちの1つ又はそれ以上を含む、レンズを制御する機能を、適切なアルゴリズムとともに画像信号プロセッサ(ISP)内に統合した効率的な画像取り込みシステムを開示する。特に、集積化したISP回路は、光学アセンブリの合焦およびズーム光学系の動きを制御したり、安定化を制御したり、フラッシュを制御したり、ズームおよび合焦レンズを制御する強化された機能および特徴を提供して、改善した画像取り込みシーケンス及び/又はレンズデータの追跡を可能にしたり、ISP内にアルゴリズムのセットを設けて、画像のアスペクト比(画像の高さと幅の両方)を変更して、例えば、アナモフィックレンズを追加したり、アナモフィックレンズをモジュールに組み込んで、焦点面アレイでの画像の投影アスペクト比を変更することができる。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]