フィリップス エレクトロニクス ナムローゼ フェンノートシャップにより出願された特許

1 - 1 / 1

III−V/II−VI半導体インターフェイス製造法

【課題】III−V/II−VI半導体インターフェイスを再現的に製造する。

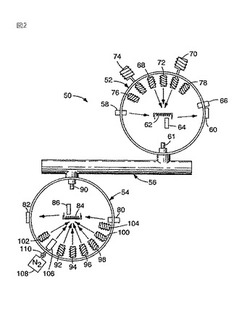

【解決手段】III族元素ソース(68、170)、II族元素ソース(72、92’)、V族元素ソース(70、172)、及びVI族元素ソースを含む分子線エピタキシー(MBE)装置(50、150)を準備する。III−V半導体表面を有する基板(12)をMBE装置(50、150)内に位置決めする。基板(12)を次にIII−V半導体成長に適切な温度まで加熱し、結晶質III−V半導体バッファ層(14)を成長させる。基板の温度を交互分子線エピタキシーによってII−VI半導体成長に適切な温度まで調整し、結晶質II−VI半導体バッファ層(16)をIII−Vバッファ層上に成長させる。II族及びVI族ソースを操作して、III−Vバッファ層をVI族元素フラックスに暴露する前にII族元素フラックスに暴露させる。

(もっと読む)

1 - 1 / 1

[ Back to top ]