ソリッド ステート ストレージ ソリューションズ インクにより出願された特許

1 - 10 / 11

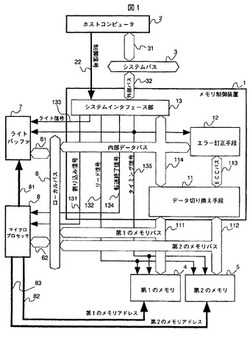

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

メモリシステム

【課題】メモリアクセスを伴うデータ処理効率向上に寄与するメモリシステムを提供する。

【解決手段】書換え可能な不揮発性メモリ(2)、バッファメモリ(5)及びコントローラ(4)を有する。コントローラは外部装置に接続される第1データ転送制御部(11)、不揮発性メモリに接続される第2データ転送制御部(12)、及び第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に応答してバッファメモリとの間のデータ転送を制御する転送調停部(13)を有する。前記第1データ転送制御部は外部装置と転送調停部に接続され、転送調停部に転送要求を出力する。第2データ転送制御部は不揮発性メモリと転送調停部に接続され、転送調停部に転送要求を出力する。転送調停部は、第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に対し、バッファメモリに対する書き込みと読み出しの転送を時分割で制御する。

(もっと読む)

不揮発性メモリ装置

【課題】回路の規模の増大を最少に抑え、短時間で高精度の書込み、読み出し、消去動作を実現可能な多値記憶型不揮発性メモリ装置を提供する。

【解決手段】不揮発性メモリ装置はクロック端子、コマンド端子、データ端子、制御回路、及び複数の不揮発性メモリセルを有する。クロック端子はクロック信号を入力する。コマンド端子は読み出しコマンド及び書込コマンドなどを入力し、入力されたコマンドはデコードされることにより動作を決める。制御回路は、プログラムメモリに格納されたプログラムを実行することにより前記コマンドに対応した動作制御を行う。読み出しコマンドの入力に応答して制御回路は不揮発性メモリセルからデータを読み出し、クロック信号に応じてデータ端子からデータを出力する。書込コマンドの入力に応答して制御回路はクロック信号に応じてデータ端子からデータを入力し、不揮発性メモリセルへデータを格納する。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、小型化、低価格化が可能で、起動時間、アクセス時間が短い大容量の半導体記憶装置を提供することを目的とする。

【解決手段】不揮発性半導体メモリに格納されるデータの誤り検出・訂正を行う誤り訂正回路と、複数のバッファを備え、誤り訂正回路による誤り検出・訂正後のデータの複数のバッファのうち、一つからホストへのインターフェイス制御回路を通じた転送と、誤り訂正回路による誤り検出・訂正のための他のデータの前記不揮発性半導体メモリから前記複数のバッファのうちの他の一つへの転送とを平行に行う。

(もっと読む)

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

半導体情報処理装置

【課題】ライトプロテクト機能のない不揮発性メモリを使用したメモリカードならびに情報処理装置において、不揮発性のソフトウェアライトプロテクトが可能な不揮発性メモリおよびそれを用いたシステム技術を提供する。

【解決手段】不揮発性のソフトウェアライトプロテクト機能のない書き換え可能な不揮発性メモリを用いたFlashメモリカード1であって、一括電気的消去および書き込み可能なFlashメモリ2と、電源投入時のパワーオンリセット信号を発生するリセットIC3と、これらのデバイス間のコントロールとメモリカードインタフェースとの間の制御を行うカードコントローラ4とから構成され、Flashメモリ2には、ライトプロテクトを行いたいエリアのアドレスをライトするライトプロテクト保存レジスタ5がアトリビュート領域で設定され、システムからプロテクト範囲が設定されるようになっている。

(もっと読む)

不揮発性メモリ

【課題】 回路の規模の増大を最少に抑え、かつ短時間で高精度の書込み、読み出し、消去動作を実現可能な多値記憶型不揮発性記憶装置を提供する。

【解決手段】 複数の不揮発性メモリセルを含むメモリアレイと、第1データレジスタと第2データレジスタとを有し、前記複数の不揮発性メモリセルのそれぞれは、しきい値電圧の状態に応じて2ビットのデータを格納可能であり、前記不揮発性メモリセルへデータを格納する書込動作において、前記不揮発性メモリセルに格納されるデータがビット毎に前記第1データレジスタと前記第2データレジスタに入力され、前記第1データレジスタから供給された1ビットのデータと前記第2データレジスタから供給された1ビットのデータとに基づいて変換された前記2ビットのデータが前記不揮発性メモリセルに格納されるようにした。

(もっと読む)

メモリシステム

【課題】メモリアクセスを伴うデータ処理効率向上に寄与するメモリシステムを提供する。

【解決手段】書換え可能な不揮発性メモリ(2)、バッファメモリ(5)及びコントローラ(4)を有する。コントローラは外部装置に接続される第1データ転送制御部(11)、不揮発性メモリに接続される第2データ転送制御部(12)、及び第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に応答してバッファメモリとの間のデータ転送を制御する転送調停部(13)を有する。前記第1データ転送制御部は外部装置と転送調停部に接続され、転送調停部に転送要求を出力する。第2データ転送制御部は不揮発性メモリと転送調停部に接続され、転送調停部に転送要求を出力する。転送調停部は、第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に対し、バッファメモリに対する書き込みと読み出しの転送を時分割で制御する。

(もっと読む)

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

不揮発性メモリ装置

【課題】回路の規模の増大を最少に抑え、短時間で高精度の書込み、読み出し、消去動作を実現可能な多値記憶型不揮発性メモリ装置を提供する。

【解決手段】不揮発性メモリ装置はクロック端子、コマンド端子、データ端子、制御回路、及び複数の不揮発性メモリセルを有する。クロック端子はクロック信号を入力する。コマンド端子は読み出しコマンド及び書込コマンドなどを入力し、入力されたコマンドはデコードされることにより動作を決める。制御回路は、プログラムメモリに格納されたプログラムを実行することにより前記コマンドに対応した動作制御を行う。読み出しコマンドの入力に応答して制御回路は不揮発性メモリセルからデータを読み出し、クロック信号に応じてデータ端子からデータを出力する。書込コマンドの入力に応答して制御回路はクロック信号に応じてデータ端子からデータを入力し、不揮発性メモリセルへデータを格納する。

(もっと読む)

1 - 10 / 11

[ Back to top ]