エクセジー・インコーポレイテツドにより出願された特許

1 - 5 / 5

コプロセッサを使った高性能のデータメタタグ付けおよびデータ索引付けの方法およびシステム

コプロセッサ(450)を使ってデータストリームのメタデータ生成をハードウェアアクセラレートする方法およびシステムが本明細書で開示される。これらの技法を使用すれば、データを高速で、豊富に索引付けし、分類し、クラスタ化することができる。コプロセッサによるこのハードウェアアクセラレーションには、フィールドプログラマブルゲートアレイ(FPGA)などの再構成可能論理(402)を使用することができる。コプロセッサがデータストリームの所望のメタデータを生成するために、完全マッチング、近似マッチング、正規表現パターンマッチングといった技法を用いることができる。 (もっと読む)

コプロセッサを使った構造化データおよび非構造化データの高性能の統合、処理および探索の方法およびシステム

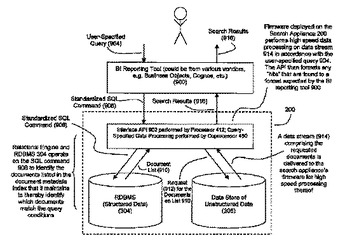

ユーザおよび企業体アプリケーションに、企業体の構造化データおよび非構造化データへの効率的で、インテリジェントなアクセスを提供するためにそれらのデータを統合する方法およびシステムが本明細書で開示される。SQLコマンドなどの標準化データベース問い合わせ形式を使って、企業体の構造化と非構造化データの両方に問い合わせを向けることができる。問い合わせを処理する必要に応じて、コプロセッサを使い、非構造化データに対する(全文検索などの)データ処理タスクをハードウェアアクセラレートすることができる。さらに、ハードウェアアクセラレートされたデータ処理のために企業体の非構造化データのどの部分がコプロセッサに送られるべきか判定するために、従来の関係データベース技術を使って、関係データベースによって格納されている構造化データにアクセスすることもできる。  (もっと読む)

(もっと読む)

近似パターン合致の方法および装置

各々のパターンが所定の許容可能な誤りを有する1つまたは複数のパターンと合致するデータセグメントについてデータストリームを検査するシステムおよび方法であって、複数の並列フィルタ機構を用いて、複数のパターンのシンボルの組み合わせに関してデータストリームをフィルタリングすることと、複数の可能性のあるパターン断片の合致を検出することと、複数の可能性のある合致パターンを特定することと、削減ステージを用いて、特定された複数の可能性のある合致パターンを、可能性のある合致パターンのセットへと削減することと、関連するデータ、および各々の合致パターンが関連する許容可能な誤りを有する、可能性のある合致パターンの削減されたセットを検証ステージに提供することと、検証ステージを用いて、複数のパターンのシンボルの組み合わせおよび関連する許容可能な誤りからデータストリームでのパターン合致の存在を検証することとを含む。  (もっと読む)

(もっと読む)

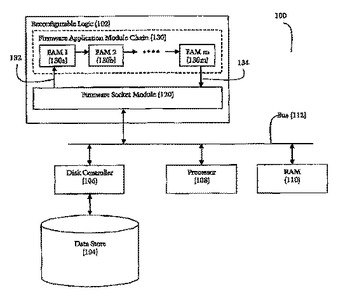

FPGAベースのパイプライン処理のためのファームウェアソケットモジュール

ファームウェアソケットモジュールが、再構成可能なロジックデバイス上に配備され、ファームウェアソケットモジュールは、ファームウェアソケットモジュールと、データ処理パイプラインへの入口点との間の通信パスを有し、ファームウェアソケットモジュールは、データ処理パイプラインの入口点に、同一の通信パスを介してコマンドとターゲットデータの両方を供給するように構成され、各コマンドは、データ処理パイプラインによって実行されるべきデータ処理動作を規定し、ターゲットデータは、データ処理パイプラインが、命令されたデータ処理動作を実行する対象となるデータに対応する。好ましくは、ファームウェアソケットモジュールは、データ処理パイプライン全体を通して保たれる所定の順序で、コマンドおよびターゲットデータを供給するように構成される。  (もっと読む)

(もっと読む)

高性能正規表現パターンマッチングのための方法および装置

本明細書では、正規表現パターンマッチングについての改良アーキテクチャが開示される。発明者らによって説明される、パターンマッチング決定性有限オートマトン(DFA)に対する改良は、状態依存のフィードバックを最終パイプラインステージに押し込めて、それによって、並列性およびスループットを向上させるパイプライン化戦略と、遷移がパターンマッチを示しているかどうかを追跡して、それによって、DFAにとって必要な状態の数を削減する拡大された状態遷移と、遷移がマッチングプロセスのリスタートを示しているかどうかを追跡する拡大された状態遷移と、DFAの遷移テーブルの圧縮と、同値類識別子への入力シンボルのアルファベット符号化と、最適化遷移テーブルメモリを可能にするためのインダイレクションテーブルの使用と、サイクル当たり複数の入力シンボルを処理するために改良DFAの能力を促進する強化されたスケーラビリティと、を含む。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]