サイコン セミコンダクター アクティエボラーグにより出願された特許

1 - 5 / 5

クロック信号発生器

【課題】集積回路のクロック信号を柔軟に発生するためのクロック信号発生器を実現する。

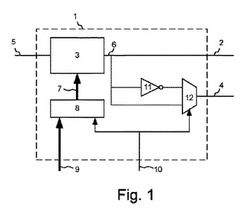

【解決手段】集積回路のクロック信号を発生するためのクロック信号発生器(1)である。クロック信号発生器は、基準クロック信号に基づいて複数の相互に遅延したクロック位相を発生するようになった遅延同期ループ(3)を備える。遅延同期ループはさらに、第1の制御信号に応答して、複数のクロック位相のうち1つを、遅延同期ループ(3)の出力信号として選択するようになっており、この出力信号は第1のクロック信号である。クロック信号発生器はさらに、出力信号の逆を発生するように配置したインバータ(11)と、クロック反転信号に応答して、出力信号かまたは出力信号の逆かのいずれかを第2のクロック信号として転送するように配置したマルチプレクサユニット(12)とを備える。

(もっと読む)

時間インターリーブ型アナログ/デジタルコンバータ

時間インターリーブ型アナログ/デジタルコンバータを動作させる方法であって、時間インターリーブ型アナログ/デジタルコンバータは、M個のサブADCのアレイを有し、Mは偶数であり、且つ、アレイの各々の列は、M個のサブADCの1つのサブADCを有する。上記方法は、全てのサンプリングインスタンスnについて、アレイの列k(n)内のサブADCによりアナログ入力を変換する段階を有し、ここで、nは、一連の整数の1つの整数であり、1≦k(n)≦Mである。第1サンプルインスタンスについて、1とMとの間の値がk(n)に割り当てられ、更に、k(n)≦M/2の場合は、k(n+1)>M/2であり、それ以外の場合は、k(n+1)≦M/2であり、且つ、M/2−1≦|k(n+1)−k(n)|≦M/2+1であり、且つ、n−mがMの整数倍である場合のみ、k(n+1)=k(m+1)となるように、k(n+1)が選択される。  (もっと読む)

(もっと読む)

フレキシブル性を有するアナログ/デジタルコンバータ

アナログ/デジタルコンバータ(1)が、入力レンジのサイズを制御するための第1レンジ制御値を生成する第1レンジ制御ユニット(100)と、入力レンジの中点を制御するための第2レンジ制御値を生成する第2レンジ制御ユニット(200)と、第1レンジ制御ユニット及び第2レンジ制御ユニットに接続された基準レベルユニット(300)とを有している。基準レベルユニットは、第1及び第2レンジ制御値に基づいて複数の基準レベルを生成する。アナログ/デジタルコンバータは、更に、第2レンジ制御ユニット(200)及び基準レベルユニット(300)に接続された比較ユニット(400)を有している。比較ユニットは、アナログ/デジタルコンバータのアナログ入力値と第2レンジ制御値との間の差と複数の基準レベルの個々のレベルとの間における比較を実行し、且つ、比較に基づいてアナログ/デジタルコンバータのデジタル出力値を生成する。  (もっと読む)

(もっと読む)

ラッチ素子

【課題】同相モード変化に対する影響の受けやすさを低減したラッチ素子を実現する。

【解決手段】第1の分岐(4a)中の第1の入力素子(10a)と第2の分岐(4b)中の第2の入力素子(10b)とを備えるラッチ素子(1)である。ラッチ素子は、第1の入力素子(10a)が生成する電流の第1の推定値を生成する第1の推定ユニット(40a)と、第2の入力素子(10b)が生成する電流の第2の推定値を生成する第2の推定ユニット(40b)とを備える。ラッチ素子はさらに、第1および第2の推定ユニット(40a、40b)に機能的に接続した制御電圧ユニット(50)を備える。制御電圧ユニットは、第1の推定値および第2の推定値の合計に基づいて制御電圧を生成する。さらに、ラッチ素子(1)は、少なくとも制御電圧に基づいて電流を生成する第1および第2の電圧制御電流ユニット(30a、30b)を備える。第1の電圧制御電流ユニット(30a)は第1の分岐(4a)に機能的に接続する。第2の電圧制御電流ユニット(30b)は第2の分岐(4b)に機能的に接続する。ラッチ素子(1)の同相モード変化を補償するための方法も開示される。

(もっと読む)

トラックホールド回路

【課題】信号対雑音歪み比(SNDR)を改善した広帯域トラックホールド回路を実現する。

【解決手段】スイッチ素子(10)および容量性保持素子(20)を備えるトラックホールド回路(1)である。トラックホールド回路(1)は、スイッチ素子(10)の入力端子の信号に基づいて制御電圧を生成し、トラックホールド回路(1)の追従段階で制御電圧をスイッチ素子(10)に供給する追従電圧生成素子(30)を備える。制御電圧は、スイッチ素子(10)において、各追従段階について同じチャネル電荷を提供する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]