シデンス・コーポレーションにより出願された特許

1 - 4 / 4

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

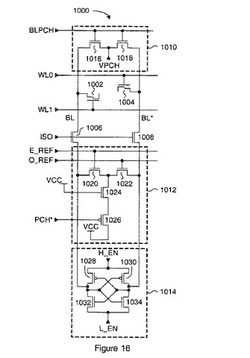

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

高速OTP感知スキーム

不揮発性メモリアレイのための高速感知スキームが開示される。メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。  (もっと読む)

(もっと読む)

マスクプログラム可能なアンチヒューズ構造

ワードライン及びビットラインに接続されると共に、マスクプログラムが可能で、かつワンタイムプログラムが可能なメモリセルを有するメモリアレイを提供する。メモリアレイの全てのメモリセルは、ワンタイムプログラム可能なメモリセルとして構成される。あらゆる数のこれらのワンタイムプログラム可能なメモリセルは、拡散マスクプログラミングもしくは接点/ビアマスクプログラミングのようなマスクプログラミングによって、マスクプログラム可能なメモリセルに変換できる。両方のタイプのメモリセルが、同じ材料で構成されるので、そのようなハイブリッドメモリアレイの製造は単純化され、従って、わずか1つの共通の製造工程のステップが必要とされる。マスクプログラム可能なメモリセルの不注意なユーザプログラミングは、プログラミングロック回路によって抑制されている。  (もっと読む)

(もっと読む)

二重機能データレジスタ

統合されたプログラム検証の機能性を有する二重機能データレジスタを提供する。二重機能データレジスタのマスタ及びスレーブラッチ回路は、2つの異なるデータのワードを同時に保存し得る。プログラム検証動作において、マスタラッチはプログラムデータを保存し、スレーブラッチは読み取りデータを受け取り保存する。各レジスタステージの比較ロジックは、双方のラッチのデータを比較し、比較結果を前段のレジスタステージの比較結果に統合する。最後の1ビットの結果は、プログラムされなかった少なくとも1ビットの存在を示す。各ステージ内の自動プログラム抑制ロジックは、首尾よくプログラムされたビットが次の再プログラムサイクルにおいて再プログラムされることを防止する。クロック信号のロウまたはハイのアクティブ状態の論理レベルにおいて、選択的にシフト動作を開始することで、いずれかのデータワードが連続してクロックに従い出力される。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]