ザイリンクス インコーポレイテッドにより出願された特許

1 - 10 / 58

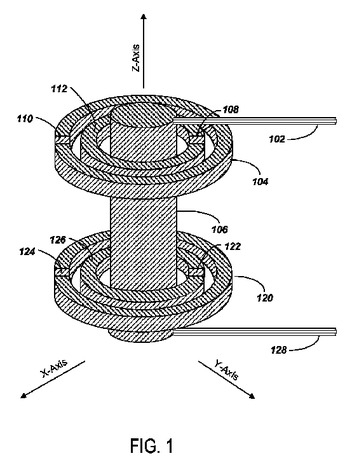

積層二重インダクタ構造

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

選択されたマッピングでアシストされたパイロットトーンのためのシステムおよび方法

通信チャネルの同じ通信サブキャリアにおけるデータ値およびパイロットトーンを通信するための方法が提供される。第1のデータ値に対応する第1の基準位相が選択される(810)。第1の基準位相を有するパイロットトーンが生成される(1414)。生成されたパイロットトーン(812)が送信される(1418)。送信されたパイロットトーンが受信される(1426)。受信されたパイロットトーンの位相が決定される(814)。受信されたパイロットトーンの位相から、第2のデータ値が決定される(816)。第2のデータ値(802)は、電子記憶媒体に記憶される。  (もっと読む)

(もっと読む)

ミラーリングされた相互接続構造を有するプログラマブル集積回路

ミラーリングされた相互接続構造を有するプログラマブル集積回路(IC)は、水平方向に配列される複数の配列(102,104)を含む。各配列は、第1のロジックコラム(106)と、第1の相互接続コラム(108)と、第2の相互接続コラム(110)と、第2のロジックコラム(112)とを含み、それらは配列内にこの順序で水平方向に配列される。各相互接続コラムは、プログラマブル相互接続ブロック(PIB130−144,188−196,199)を含み、第1および第2のロジックコラムの各々は、プログラマブルロジックブロック(114−128,164−171)を含む。各プログラマブル相互接続ブロックは、一側面に複数の入力ポート(174)および出力ポート(172)を提供する。各プログラマブルロジックブロックは、一側面に第2の入力ポート(156)および出力ポート(158)を提供する。第1の相互接続コラム(108)におけるプログラマブル相互接続ブロックの各々の第1のポートおよび一側面は、第2の相互接続コラム(110)における各プログラマブル相互接続ブロックの第1のポートおよび一側面を物理的にミラーリングする。第1の相互接続コラム(108)におけるプログラマブル相互接続ブロックの第1のポート(172,174)は、第1のロジックコラムにおけるプログラマブルロジックブロックの第2のポート(156,158,182,184,186,190,194)に結合される。第2の相互接続コラム(110)におけるプログラマブル相互接続ブロックの第1のポートは、第2のロジックコラムにおけるプログラマブルロジックブロックの第2のポート(160−162,172−180,198)に結合される。  (もっと読む)

(もっと読む)

マルチチップ集積回路

複合集積回路(IC,100)は、再構築ウェハベース(108)上において、第1のオンチップ相互接続構造(114)を有する第1のICダイ(チップ,102)と、第2のオンチップ相互接続構造(115)を有する第1のICダイ(104)とを結合する。第2のICダイは、第1のICダイと酸化物−酸化物端部接合(110)を用いて端部接合される。チップトゥチップ相互接続構造(118)は、第1のICダイと第2のICダイとを電気的に結合する。このような複合ICを製造するための方法も説明される。  (もっと読む)

(もっと読む)

集積回路における相互接続レイアウトのための方法および装置

実施形態は、集積回路(IC)を設計する方法(たとえば、コンピュータで実現される方法)に関する。この実施形態において、基板(402)上の集積回路の導電層(404−1,404−2,404−3,404−4,404−5)を記述するレイアウトデータ(400)が、集積回路のための設計仕様データに従って生成される。導電層は、ボンディングパッド(406)の最上層を含む。レイアウトデータにおける金属構造体(408)が変更されて、各々のボンディングパッド(406)の下の閾値体積内の導電層(404−1,404−2,404−3,404−4,404−5)の重畳した平面内における金属密度を最大化する。レイアウトデータ(400)の記述は、集積回路を製造するための1以上のマスクに生成される。重畳した平面内における金属密度を最大化することにより、相互接続体における誘電性材料(412)を通る縦方向チャネルが減少される、あるいはなくなる。したがって、α粒子が容易に相互接続体を貫通して下部の基板(402)に達することができなくなり、メモリセルにおけるシングルイベントアップセットのようなソフトエラーを減少させる。  (もっと読む)

(もっと読む)

QR分解およびシストリックアレイを用いたMIMO最小二乗平均誤差受信器

第1のシストリックアレイ(210,400,612,712)は、複数のチャネル行列(202)から、時分割多重化された行列の入力セット(H,HAB)を受信する。第1のモードにおいては、第1のシストリックアレイは、入力行列について三角行列化(508)を実行して第1の行列セットを生成し、第2のモードにおいては、第1のセットについて後退代入(510)を実行して第2の行列セット(R-1)を生成する。第1のモードにおいては、第2のシストリックアレイ(220,1100,616、716)は、第2の行列セットについて入力行列セットを用いて左乗算(512)を実行して、第3の行列セットを生成する。第2のモードにおいては、第2のシストリックアレイは、第3の行列セットについてクロス対角変換(513)を実行して、第4の行列セット(Q1’)を生成するとともに、第2の行列セットについて第4の行列セットを用いて右乗算(514)を実行する。第1のシストリックアレイは、三角化行列の後に第1のモードから第2のモードへ切り換わり、第2のシストリックアレイは、左乗算の後に、第1のモードから第2のモードへ切り換わる。  (もっと読む)

(もっと読む)

スペクトル検出を用いたフェムトセル構造

実施形態は、スペクトルチャネルの選択のための、スペクトル検出を用いるフェムトセル(104)のアドホック構造を提供する。この実施形態においては、指定場所(130)においてマクロセルによって予約されていない周波数帯が決定されるとともに、スペクトル検出(206〜220)が実行されて、範囲内の他のフェムトセルによって用いられている未予約の周波数帯における通信チャネル(306)が決定される。このように、フェムトセルは、配置されたフェムトセル間の外部の調整または制御なしに、アドホック方式で配置および構成され得る。  (もっと読む)

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

高インピーダンスの電気接続ビア

一般的に、ビア(106)のインピーダンスは自身に接続された信号線(102、128)よりも低い。ノイズおよび反射信号が原因でインピーダンス不整合が生じると、回路を、所望の周波数よりも大幅に低い周波数で動作させる必要が生じることがある。ある実施の形態は、回路内のインピーダンス不整合を回避し、スプリットリング共振器(104、112、120、126)をビア(106)の各端部に追加してビア(106)のインピーダンスをより高くすることにより、当該技術における進歩を遂げる。  (もっと読む)

(もっと読む)

集積回路出力ドライバ用の共有静電放電保護

集積回路(IC)内の金属酸化膜半導体電界効果トランジスタ(MOSFET)出力ドライバを静電放電(ESD)から保護するためのシステムは、共通のIC拡散材(205)内に位置付けられる第1のMOSFET出力ドライバおよび第2のMOSFET出力ドライバを含む。本システムは、共通IC拡散材に結合され、MOSFET出力ドライバを囲む外周の外縁に沿って配置されるコンタクトリング(225,325,420)を含む。各MOSFET出力ドライバのセントロイドは、両方のMOSFET出力ドライバを囲む外周のセントロイド(385,460)と共通である。各MOSFET出力ドライバは、バイポーラスナップバックをESD事象が起こるMOSFET出力ドライバで開始させる値のRsub(基板抵抗275および280)を有する。Rsubの値は、各MOSFET出力ドライバのセントロイドからコンタクトリングまでの合成距離に依存する。  (もっと読む)

(もっと読む)

1 - 10 / 58

[ Back to top ]