アナログ デバイセス インコーポレーテッドにより出願された特許

1 - 10 / 18

可変利得増幅システム

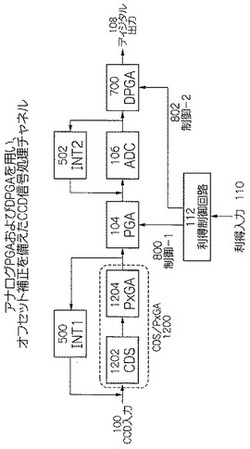

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

可変利得増幅システム

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】積分器を備えることによって、相関二重サンプリング回路の入力およびプログラマブル利得増幅器の出力において、補正を行なう。プログラマブル利得増幅器に利得制御機能を備える。第2積分器は、全ディジタルとすることも、あるいはアナログおよびディジタル信号を組み合わせることも可能である。また、ディジタル・プログラマブル利得増幅器を用いて、前述のチャネルを構成することも可能である。ディジタル・プログラマブル利得増幅器は、信号処理チャネルにおいてアナログ・プログラマブル利得増幅器と組み合わせることができる。

(もっと読む)

チョッパ安定化増幅器内のオフセットおよびリップルの抑制のための自動補正フィードバックループ

チョッパ安定化増幅器は、相互コンダクタンス増幅器の入力および出力において第1のチョッピング回路と第2のチョッピング回路とを有する主信号経路と、自動補正フィードバックループとを含む。このフィードバックループは、主信号経路からチョッピングされた出力を増幅するために接続された相互コンダクタンス増幅器と、増幅された出力をチョッピングする第3のチョッピング回路と、フィルタリングされている信号内に存在する任意のオフセット電圧誘起AC成分を実質的に削減するために、チョッピングされた出力をフィルタリングするフィルタと、フィルタリングされた出力を受信して、主信号経路に結合し戻された出力を生み出す相互コンダクタンス増幅器と含む。 (もっと読む)

ドレインおよび/またはソース変形注入物を有するJFET

本発明は、製作中に追加の注入物を受け取るJFETを提供する。この注入物は、JFETのドレイン領域をそのソース領域の方へ延ばし、かつ/またはそのソース領域をそのドレイン領域の方へ延ばす。注入物は、ドレイン/チャネル(および/またはソース/チャネル)接合部で所与のドレイン電圧および/またはソース電圧に対して普通なら生じるはずの電界の大きさを低減させ、それによって電界に関連するゲート電流および降伏の問題の重大度を軽減する。JFETのゲート層は、各注入物に対して、ゲート層の横方向の境界とドレイン領域および/またはソース領域との間にそれぞれ間隙を設ける幅を有するように寸法設定され、各注入物がそれぞれの間隙内に注入されることが好ましい。 (もっと読む)

大信号出力ブースト段を備えた小信号増幅器

大信号出力ブースト段を備えた小信号増幅器は、第1の電源レールと第2の電源レールとの間に接続されている(vIII)。小信号増幅器は、第1および第2の入力信号(INP、INM)を受け取り、負荷をドライブする出力接続点に出力信号を提供している。小信号状態下では、出力信号は差動電圧に応じてほぼ直線的に変化する。しかしながら、大信号状態下では、出力接続点(14)に接続されたレール−レール大信号出力ブースト段は、負荷によって要求される電流を必要に応じて提供するために、第1または第2の電源レールの近くに出力接続点をドライブするようになされている。大信号出力ブースト段は、小信号状態ではオフであるが、大信号状態の下では急激にオンになり、最大電荷が負荷に引き渡される。 (もっと読む)

タイマ回路および方法

タイミング回路は、任意の電圧を抵抗(R1)の両端間に加え、その結果として生じる電流を、キャパシタンス(C1)を端点電圧に充電および/または放電する充電電流を生成するために使用することによって動作する。抵抗の端点電圧の一方に比例する閾値をキャパシタンスの電圧が横切るまで、キャパシタンスの端点電圧が抵抗の端点電圧を追跡するようなやり方でキャパシタンス(C1)が充電および/または放電されるように、追加の回路は構成される。したがって、抵抗器の電圧は、供給電圧または温度に関係して変化してもよく、または抵抗値自体がタイミング関係に重大な影響を及ぼすことはなく変化することがある。任意の電圧は、好ましくは、抵抗(R1)と直列に接続された一対のダイオード接続トランジスタ(MP1、MN1)で供給され、その結果、そのダイオード接続トランジスタの一方と同じ電流密度で動作される単一のトランジスタが閾値電圧を確定し、かつコンデンサ電圧がこの閾値に達したときを検出するようになる。 (もっと読む)

電荷再分布型アナログ/ディジタル・コンバータのパワーアップ校正

【課題】アナログ・ディジタル・コンバータ集積回路におけるパワーアップ遅延回路を用いてパワーアップから遅延信号を生成し、遅延信号の検出と同時にコンバータの校正を開始する。

【解決手段】集積回路の校正入力ピンにおける信号に応答して校正を開始することもでき、遅延の持続時間は、(例えば、外部コンデンサを基準により充電することにより)基準から、あるいは校正動作の持続時間から得ることができる。集積回路が変換中または校正中でない時この集積回路を遮断モードに保持するパワーアップと同時に回路を動作モードに自動的にいれる回路を提供することができる。

(もっと読む)

ソースバイアス式メモリセルアレイ

メモリセルアレイは、バイアス電圧が、その「オフ」状態漏れ電流が減るように、メモリセル(100)内の1つまたは複数のFETのソースに印加される、「ソースバイアス」を使用する。ソースバイアス電圧は、「オフ」FETの場合の小さな正のバイアスとFETが読み出される場合のアースの間で選択的に切り換えられる。複数のソースバイアス回路(110、112、114、116)は、選択的に切り換えられたバイアス電圧を、アレイのメモリセルに供給する。  (もっと読む)

(もっと読む)

高/低同相モード入力電圧のための独立入力オフセット補正機能付演算増幅器

高/低同相モード入力電圧のためのVos独立補正機能を提供する演算増幅器である。該演算増幅器は、相補型入力対(MP1/MP2、MN1/MN2)を含み、Vcmが閾電圧Vthよりも低いときはバイアス電流Itailを一方の対に供給し、Vcmが閾電圧Vthよりも高いときはItailを他方の対に供給するステアリング回路(24)を採用している。入力対は、1つまたは複数のトリム入力(TRIM1、TRIM2)を含む負荷段(14)を駆動し、トリム入力は、印加される1つまたは複数の補正信号に応答してVosが変化することを可能にする。第一の補正信号発生回路(26)は、VcmがVthよりも低いときのみ第一の補正信号(ΔI1)を供給し、第二の補正信号発生回路(28)は、VcmがVthよりも高いときのみ第二の補正信号(ΔI2)をトリム入力に供給する。これにより、入力同相モード電圧Vcmが高いときも低いときも、入力オフセット電圧を独立して調整することが可能となる。  (もっと読む)

(もっと読む)

交差伝導防止ドライバ制御回路および方法

交差伝導防止ドライバ回路および方法は、競合状態の発生を防止し、本発明に従って制御される、典型的にはMOSFETの、直列接続電力デバイス間の交差伝導を回避する。個々の状態機械が、各電力デバイスドライバの入力と出力の間に接続され、ドライバが要求されたタスクを完了した時点を正確に決定するように構成される。各状態機械は、ドライバステータスに基づいて「ロックアウト」信号を生成し、この信号は、指定条件下において反対側ドライバの動作を禁止し、それによって、直列接続電力デバイス間の交差伝導を防止するために使用される。  (もっと読む)

(もっと読む)

1 - 10 / 18

[ Back to top ]