モーセッド・テクノロジーズ・インコーポレイテッドにより出願された特許

1 - 10 / 15

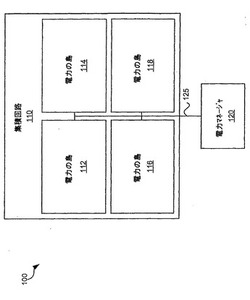

電力の島を使用した集積回路での電力の管理

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

電力の島を使用した集積回路での電力の管理

【課題】集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

半導体メモリ非同期式パイプライン

【課題】非同期式パイプライン型半導体メモリを提供する。

【解決手段】非同期にパイプラインされるSDRAMは、非同期信号によって制御される別個のパイプライン段を有する。各段でデータを同期させるためにクロック信号を使用するのではなく、すべての段でデータをラッチするために非同期信号28が使用される。非同期制御信号はチップ内に生成され、そして異なった待ち時間段27に最適化される。データは、チップから読み出される前の読み取りデータパス24の終わりでクロックに同期させられる。データは各パイプライン段でラッチされているので、データに生じるスキューは、従来のウェーブパイプラインアーキテクチャに見られるよりも小さい。さらに、段はシステムクロックCLKと無関係であるので、読み取りデータパスをサポートするために再同期出力を形成するだけで、読み取りデータパスを任意のCAS待ち時間で処理することができる。

(もっと読む)

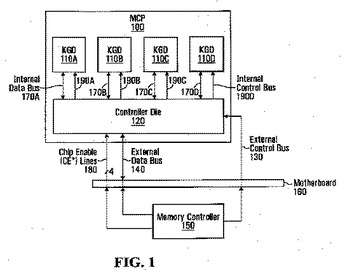

複数のメモリダイとコントローラダイとを有する半導体記憶装置

半導体記憶装置は、複数のメモリダイと、コントローラダイとを含む。コントローラダイは内部制御バスに接続される。コントローラダイは、外部リードコマンドに応答して、前記メモリダイのうちの選択された1つに内部リードコマンドを提供するように構成される。選択されたメモリダイは、内部リードコマンドに応答して、コントローラダイに読み出しデータを提供するように構成される。選択されたメモリダイとして選択されたときの、コントローラダイによる外部リードコマンドの受信とコントローラダイによる該選択されたメモリダイからの読み出しデータの受信との間のレイテンシが、前記メモリダイのうちの少なくとも2つに関して相異なる。  (もっと読む)

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

半導体メモリ非同期式パイプライン

【課題】非同期式パイプライン型半導体メモリを提供する。

【解決手段】非同期にパイプラインされるSDRAMは、非同期信号によって制御される別個のパイプライン段を有する。各段でデータを同期させるためにクロック信号を使用するのではなく、すべての段でデータをラッチするために非同期信号が使用される。非同期制御信号はチップ内に生成され、異なった待ち時間段に最適化される。データは、チップから読み出される前の読み取りデータパスの終わりでクロックに同期させられる。データは各パイプライン段でラッチされているので、データに生じるスキューは、従来のウェーブパイプラインアーキテクチャに見られるよりも小さい。さらに、段はシステムクロックと無関係であるので、読み取りデータパスをサポートするために再同期出力を形成するだけで、読み取りデータパスを任意のCAS待ち時間で処理することができる。

(もっと読む)

周波数逓倍回路

【課題】インタフェースクロックまたは外部クロックの倍数である内部クロックを発生できる周波数逓倍回路を提供する。

【解決手段】遅延ラインは、リファレンスクロックの一周期に一致するように設けられた複数の遅延素子を備え、リファレンスクロックを一端で受けて、遅延素子のそれぞれから遅延段タップ出力を発生する。複数のクロック合成回路は、それぞれ対になった複数のタップ出力に応答して、対のそれぞれから出力クロックパルスの立ち上がりエッジおよび立ち下がりエッジを発生させ、このとき、出力クロックの周期は入力クロックの周期より短い。

(もっと読む)

フラッシュメモリデバイスでの電力供給及びシステム

フラッシュメモリデバイスでの電力供給が開示される。フラッシュメモリデバイスの第1部分は、データを記憶する不揮発性メモリを有する。フラッシュメモリデバイスの第2部分は、少なくとも第1ポンプ回路及び第2ポンプ回路を有する。第1ポンプ回路は第1電圧を受け、その出力で、第1電圧レベルより高い第2電圧レベルにある第2電圧を生成する。第2ポンプ回路は第1ポンプ回路の出力に結合された入力を有し、第1電圧より大きい電圧から高めるよう第1ポンプ回路を協働して用いて、第2電圧レベルより高い第3電圧レベルにある第3電圧を生成する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

2のべき乗でないメモリ容量を有する不揮発性メモリが開示される。不揮発性記憶装置は少なくとも1つのプレーンを含む。プレーンは、各ブロックが多数のページに分割されている複数のブロックを含む。これらブロックの各々は、第1の次元に沿って、データを格納する第1の数のメモリセルによって定められ、第2の次元に沿って、データを格納する第2の数のメモリセルによって定められている。当該不揮発性メモリは、プレーンのメモリセルの総数と比例関係にある2のべき乗でない容量を有する。当該不揮発性メモリはまた、複数のローデコーダを含む。当該記憶装置内で、ページの数に対するローデコーダの数に関して、少なくとも実質的に1対1の関係が存在する。複数のローデコーダの各々は、当該記憶装置の関連するページ上での読み出し動作を促すように構成される。  (もっと読む)

(もっと読む)

電力削減機能を有する不揮発性半導体メモリデバイス

不揮発性半導体メモリデバイスは、(i)入力クロックを受信するための入力、および消去命令を含むコントローラ発行の命令を受信するための一組のデータラインを有するインターフェースと;(ii)フィードバックループ構造の回路構成要素を有し、かつ基準クロックによってドライブされるモジュールと;(iii)基準クロックが入力クロックをトラッキングする第1の状態と、基準クロックが入力クロックから切り離される第2の状態との間で制御可能に切り換えするクロック制御回路と;(iv)命令を認識し、かつ、消去命令を認識することに応答して、クロック制御回路を、基準クロックが入力クロックをトラッキングする第1の状態から、基準クロックが入力クロックから切り離された第2の状態に切り換える、命令処理ユニットと;を有する。基準クロックが入力クロックから切り離されている場合には、基準クロックが入力クロックをトラッキングしている場合より、モジュールは、より少ないパワーを消費する。  (もっと読む)

(もっと読む)

1 - 10 / 15

[ Back to top ]