Spansion Japan株式会社により出願された特許

1 - 10 / 16

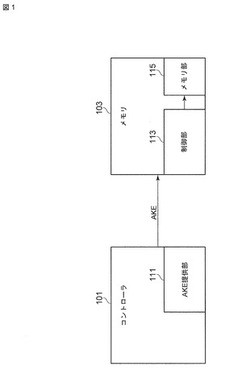

電子機器、及び、電子機器システム。

【課題】電子機器に入力される認証情報の漏洩の危険性を低減する。

【解決手段】コントローラ101に接続されたメモリ103であって、前記コントローラ101に接続される外部インタフェースと、認証情報AKEを前記コントローラ101から前記外部インタフェースを介して受信する制御部113とを有し、前記認証情報AKEは、第1値を有し、前記第1値は、第1パラメータ値又はそれの基になる値であり、前記制御部113は、前記認証情報AKE内の前記第1値に従う第1パラメータ値を用いた制御を行う。

(もっと読む)

メモリ装置

【課題】異なる種類のメモリを積層させたメモリ装置を提供する。

【解決手段】メモリ装置100は、互いに異なる種類の2つのメモリセルアレイを積層して構成されたメモリセルアレイ10を備える。互いに異なる種類の2つのメモリセルアレイそれぞれには、それぞれに対応するワード線が上記マトリクスの行方向に延設されている。また、互いに異なる種類の2つのメモリセルアレイにおける上記マトリックスの列方向に延設されたデータ転送線は、互いに異なる種類の2つのメモリセルアレイにおいて共用されている。メモリ層選択部26は、互いに異なる種類の2つのメモリセルアレイのいずれか一方を選択する。Xデコーダ25は、メモリ層選択部26の選択にしたがって、それぞれに対応するワード線を通じて互いに異なる種類の2つのメモリセルアレイに各処理に応じた電圧を供給する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 データの出力方向に柔軟性を持たせながら、小型化を図ることを可能とする不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置は、複数のメモリプレーンに跨ってワード線方向に沿って延びるワード線方向データバス線と、ワード線方向データバス線とビット線とを電気的に接続するか否かを切り替えるビットストリング選択回路と、ワード線方向データバス線に接続されるサブラッチ回路とを備える。ワード線方向データバス線、ビットストリング選択回路及びサブラッチ回路は、複数のメモリ領域の間においてワード線方向に沿って延びる帯状領域に設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 特定の処理に続けて読み出されるデータを任意に指定することを可能とする不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置は、第1メモリ領域及び第2メモリ領域を少なくとも含むメモリ領域を有する。不揮発性半導体記憶装置は、前記第1メモリ領域に対する処理の実行を指示する特定コマンドに応じて、前記第1メモリ領域に対する処理が行われる場合に、前記第1メモリ領域に対する処理に続けて、前記第2メモリ領域に格納されたデータを読み出すように構成された制御部を備える。前記特定コマンドは、前記第1メモリ領域に対する処理に続けて、前記第2メモリ領域に格納されたデータを読み出すべきことを識別する識別情報を含む。

(もっと読む)

不揮発性半導体メモリ装置及び不揮発性半導体メモリ装置のデータ読み出し方法

【課題】読み出し時にビット線を流れる電流を削減し、消費電力の向上を図ると共に、充放電電流の集中による動作不具合を回避できるようにする。

【解決手段】メモリセルアレイ1は、メインデータ線MDLからビット線BLが分岐された階層構造となっており、メインデータ線MDLとビット線BLとの間に、反転センス回路10が挿入される。反転センス回路10は、データの読み出し時に、ビット線BLのデータをセンスすると共に、上層側のメインデータ線MDLと下層側のビット線BLとの間で一方に電流が流れるときに他方に電流が流れないように設定する。これにより、ビット線の寄生容量が減少し、読み出し時の消費電力の低減が図れると共に、データ「1」の場合に充放電する寄生容量と、データ「0」の場合に充放電する寄生容量が平坦化され、電流のピークが相殺され、ピーク電流のばらつきが少なくなる。

(もっと読む)

不揮発性半導体メモリ装置及び不揮発性半導体メモリ装置のデータ書込み方法

【課題】NAND型フラッシュメモリで、データ書き込み時のビット線容量及びプリチャージ電力を削減でき、また、データ書き込みを効率的に行う。

【解決手段】メモリプレーンをビット線方向に複数のデータエリアに分割し、各データエリアの分割部毎に、隣り合う各データエリア間を接続する接続線の接続または非接続を選択するサブセレクトトランジスタTSL、並びにサブラッチセレクトトランジスタSLSELを介して上記接続線に接続されたサブラッチを設ける。書き込み対象データエリアをプリチャージした後に、サブセレクトトランジスタTSLをオフさせて書き込み対象データエリアを隣り合うデータエリアと分断させる。次に、サブラッチセレクトトランジスタSLSELをオンさせてサブラッチにラッチされたデータを書き込み対象データエリアに出力させた後に、所望のページにその出力データを書き込む。

(もっと読む)

不揮発性半導体メモリ装置、およびデータ消去方法

【課題】1メモリプレーンを複数のウェルに分割して構成させた不揮発性半導体メモリ装置を提供する。

【解決手段】メモリプレーンA0は、データエリア0〜データエリア3と、スロット0〜スロット3とを備える。データエリア0〜データエリア3はデータを記憶する領域であり、複数のメモリセルをビット線方向に直列接続してなるストリングを少なくとも1つ含んでいる。データエリア0〜データエリア3はそれぞれ別のウェルにより構成されており、スロット0〜スロット3を介して直列に接続されている。ウェル電圧印加部15は、制御部12等からのウェル電圧に関する印加指示に基づいて、データエリアを構成するウェルにデータ消去電圧であるウェル電圧を印加する。この際、スロット0〜スロット3は、ウェル電圧が印加されるデータエリアと隣り合うデータエリアとの接続を切断する。

(もっと読む)

不揮発性半導体記憶装置及びその読み出し方法

【課題】読み出し動作を高速化できる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1Bは、ビット線方向B及びワード線方向Wに複数のメモリセルが配列され、ロウデコーダ101及びカラムデコーダによって制御対象メモリセルが指定されるメモリプレーン110を有する。メモリプレーン110は、少なくとも1つのメモリセルが接続されており、ビット線方向Bに沿って延びる複数のビット線BLと、少なくとも1つのビット線BLが設けられた複数のメモリセルエリア111〜114と、複数のメモリセルエリア111〜114毎に設けられた複数のサブラッチ回路SUBLATとを備える。複数のサブラッチ回路SUBLATのそれぞれは、自回路と対応するメモリセルエリアに設けられたビット線BLの電位を検出して、検出結果を保持する。

(もっと読む)

半導体装置

【課題】

プログラム動作で消去が起こってしまうという現象を避けることができる半導体装置を提供する。

【解決手段】

複数の異なるしきい値を有するメモリセルを含むメモリ部と、入力された書き込みデータを書き込もうとするメモリセルから既存データをベリファイ用センスアンプを利用して読み出す読出回路と、前記書き込みデータと前記メモリセルの既存データを比較し、書き込み動作で消去動作が起こるパターンを検出する検出回路とを有する半導体装置である。書き込み動作で消去動作が起こるパターンを禁止動作とし、この禁止動作が認識されると書き込みコマンドによる書き込み動作を開始せずに強制終了させる。

(もっと読む)

半導体装置の製造方法

【課題】一回の焼付けによりショット内の像面傾斜をモニタリングすることを可能とすること。

【解決方法】

本発明は、露光領域で囲まれた非露光領域を有する第1のパターンと、非露光領域で囲まれた露光領域を有する第2のパターンとの対を有する複数のモニタリング用マークを直線的に配置したフォトマスクを用いて被露光基板に露光をするステップと、モニタリング用マークの寸法を計測して、その値が一直線上にあるか否かによりベスト・フォーカス条件となる点があるかを判断するステップと、ベスト・フォーカス条件となる点がある場合は、モニタリング用マークの寸法を垂直方向の変位に変換するとともに、変換した垂直方向の変位のうち一直線上にない垂直方向の変位については符号を反転させ、符号を反転させない垂直方向の変位と符号を反転させた垂直方向の変位とから露光領域の像面傾斜を算出するステップと、を有する半導体装置の製造方法である。

(もっと読む)

1 - 10 / 16

[ Back to top ]