エクサー コーポレーションにより出願された特許

1 - 3 / 3

単一電圧源CMOSのための自動検出入力回路

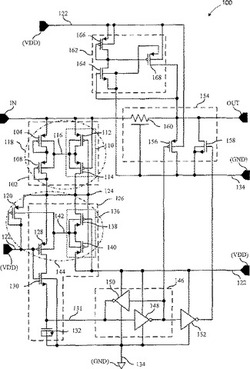

【課題】入力パッドに印加される比較的高電圧を維持し、回路内の供給電圧範囲の対応する信号レベルを生成する。

【解決手段】入力回路は、フローティングウェルと、対応するバイアスセレクタと、入力バイアストランジスタとを有し、予め定められた値より大きい電圧を維持する外部電圧にゲート酸化膜がさらされないようにする。バイアスセレクタは、利用可能な最高電圧を選択してフローティングウェルに対応するバイアスを逆にし、トランジスタに過度な電気的ストレスがかからないようにする。入力に関連する端子が関連する電圧を切り換えられると、バイアスセレクタは、別の端子を選択し、引き続き利用可能な最高電圧を選択して正しい逆バイアス条件を提供する。抵抗器およびクランプは、回路内の供給電圧範囲に制限された、変換された出力電圧レベルを生成する。ラッチ出力により、プルダウントランジスタは、正確なロウレベル出力信号を提供できる。

(もっと読む)

単一電圧源CMOSのためのオープンドレイン出力バッファ

【課題】オープンドレイン出力バッファは、出力パッドに印加される比較的高電圧を受ける。

【解決手段】オープンドレインバッファは、多数のフローティングウェルと、出力スイッチングデバイスと、対応するウェル・バイアスセレクタとを有し、ゲート酸化膜が予め定められた値より大きい電圧を受けないようにする。PMOSおよびNMOSウェル・バイアスセレクタは、それぞれ、有効な最高または最低電圧を選択して印加し、対応するウェル領域をバイアスし、デバイススイッチング端子に過剰な電気的ストレスがかからないようにする。端子関連出力にスイッチング関連電圧が印加されると、ウェル・バイアスセレクタは、代わりの端子を選択して最高または最低電圧の選択を連続して行い、適正なウェルバイアス状態を提供する。分圧器は、ウェルバイアス電圧を適正に選択させる基準電圧をフローティングウェルに対して生成する。

(もっと読む)

高速差分抵抗電圧デジタルアナログ変換器

一部分において、レジスタ、及び少なくとも2つの復号段を有する差動デジタル/アナログ変換器(VDAC)であり、レジスタはN個の区分に均等に分割され、各区分は、N個のデコーダのそれぞれに設けられることにより第1の復号段が形成され、各デコーダおけるレジスタ区分は、さらにM個の区分に均等に分割されることにより、M個のタップノードが形成される。第1の復号段における各々のデコーダは、M個のタップされた電圧のうちの2つを、N個の均等レジスタ区分のうちのレジスタ区分の中心における電圧に対する補助電圧として、対応する一組の出力ノードへと供給する。第2復号段は、N個のデコーダの各々により供給された第1の電圧及び第2の電圧を受け取り、これらの2つの電圧を、レジスタの中心における電圧に対する補助電圧として、1組の第3の出力ノード及び第4の出力ノードへと供給する。 (もっと読む)

1 - 3 / 3

[ Back to top ]