Fターム[4M118FA11]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 過剰電荷排出・吸収領域 (628)

Fターム[4M118FA11]の下位に属するFターム

オーバーフロードレイン (561)

ダミー転送路による排出 (7)

通常転送路による排出 (10)

信号線による排出 (4)

再結合領域の利用 (1)

電位障壁の利用 (31)

Fターム[4M118FA11]に分類される特許

1 - 14 / 14

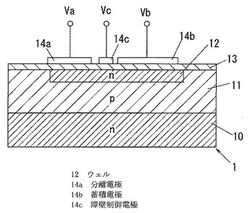

光検出素子、光検出素子の制御方法

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

撮像素子

【課題】光強度に対するダイナミックレンジの自由度を、より拡大する。

【解決手段】各画素21は、受光した光の光量に応じて電荷を発生するフォトダイオード22と、フォトダイオード22から出力される電荷を蓄積するフローティングディフュージョン24と、フローティングディフュージョン24に蓄積されている電荷をリセットするリセットトランジスタ27とを少なくとも有する。また、4つの画素21が組み合わされて疑似画素20が構成される。そして、疑似画素20では、所定の露光順番で露光が行われ、露光順番に従って、先に露光する画素21のフローティングディフュージョン24の電荷蓄積容量まで電荷が蓄積されると、次に露光する画素21のリセットトランジスタ27によるリセット動作が解除される。本発明は、例えば、CMOSイメージセンサに適用できる。

(もっと読む)

光検出素子、光検出素子の制御方法、空間情報の検出装置

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

固体撮像装置,固体撮像装置の駆動方法及び撮像装置

【課題】水平電荷転送時に余剰電荷排出領域に信号電荷が漏れ出ることを防止し、水平電荷転送領域の位置によらず一定の飽和電荷量を維持でき、シェーディングなどの画像のムラの発生を防止できる固体撮像装置及び撮像装置を提供する。

【解決手段】固体撮像装置10は、撮像領域において垂直方向及び水平方向に配列され、入射光に応じて信号電荷を生成する複数の光電変換部21と、光電変換部21で生成された信号電荷を垂直方向に転送する垂直電荷転送領域20と、垂直電荷転送領域20から転送された信号電荷を水平方向に転送する水平電荷転送領域22と、水平電荷転送時に水平電荷転送領域22に生じた余剰の信号電荷を排出する余剰電荷排出領域24と、水平電荷転送前に水平電荷転送領域22に蓄積された信号電荷の一部を排出することで飽和電荷量を低下させる飽和電荷排出手段を備えている。

(もっと読む)

固体撮像装置

【課題】従来の固体撮像装置には、過剰電荷の逃がし易さという面で向上の余地がある。

【解決手段】固体撮像装置1は、半導体基板10(第1の半導体層)、半導体層20(第2の半導体層)、および受光部30を備える裏面入射型の固体撮像装置である。固体撮像装置1は、半導体基板10の裏面S2に入射した光を光電変換することにより、被撮像体を撮像する。この半導体基板10は、比抵抗ρ1(第1の比抵抗)をもっている。半導体基板10の表面S1上には、半導体層20が設けられている。この半導体層20は、比抵抗ρ2(第2の比抵抗)をもっている。ここで、ρ2>ρ1である。半導体層20中には、受光部30が形成されている。この受光部30は、上記光電変換により生じた信号電荷を受ける。

(もっと読む)

固体撮像装置

【課題】 読み出し線の近傍に新たな回路を追加することなく、高輝度被写体の黒沈みを改善する。

【解決手段】 本発明の固体撮像装置は、下記構成を備える。単位画素は、画素配列されて基準信号および光電変換信号を順次出力する。スイッチ素子は、単位画素内に設けられて単位画素の出力を読み出し線に接続する。走査回路は、走査シーケンスに従ってスイッチ素子に選択電位を与えることで走査出力を実施する。さらに、走査回路は、基準信号を走査出力する場合、非選択状態のスイッチ素子の少なくとも一部に、選択電位と非選択電位の中間電位を与える。

(もっと読む)

撮像装置

【課題】端部の画素電極に流入する信号電荷を正確に制御することが可能な撮像装置を提供する。

【解決手段】このCMOSイメージセンサ(撮像装置)100は、複数の画素電極15aと、複数の画素電極15a上に配置された光電変換膜16と、複数の画素電極15aの端部に形成され、複数の画素電極15aの端部近傍において光電変換膜16により発生された電荷を排出するためのダミー電極15bと、ダミー電極15bに流入した電荷の排出を制御するための電荷排出用トランジスタ301とを備えている。

(もっと読む)

画像処理装置及び画像処理方法

【課題】混色の発生を抑制しながら広いダイナミックレンジを得ることができる画像処理装置及び画像処理方法を提供する。

【解決手段】入力してきた光信号を電荷に変換する受光素子部601と、受光素子部601から溢れ出た信号を蓄積する浮遊拡散層部603と、を含む複数の画素が設けられている。更に、浮遊拡散層部603に蓄積された電荷を飽和光量信号として読み出す飽和光量信号読出手段と、前記飽和光量読出手段により読み出された飽和光量信号における混色を補正する混色補正手段と、前記光電変換手段に蓄積された電荷を受光信号として読み出す受光信号読出手段と、前記混色補正手段による補正後の飽和光量信号と前記受光信号読出手段により読み出された受光信号とを合成する合成手段とが設けられている。

(もっと読む)

固体撮像装置、固体撮像装置の駆動方法および撮像装置

【課題】低照度にて通常飽和レベルを狭めることなく線形かつ高S/Nでの信号取得を可能にするとともに、通常飽和レベル以上の入射光に対しても線形領域での良好なS/Nを実現しながらダイナミックレンジを拡大する。

【解決手段】フォトダイオード21および当該フォトダイオード21で光電変換された信号電荷を転送する転送トランジスタ22を含む単位画素20が行列状に2次元配置されてなるCMOSイメージセンサ10において、転送トランジスタ22の制御電極に複数の制御電圧を供給電圧制御回路13から順次供給し、その際に転送トランジスタ22によって転送される信号電荷を2回以上読み出す駆動を垂直走査回路12によって行う。

(もっと読む)

固体撮像素子

【課題】画像データの生成に利用しない電荷の掃き出し処理を速やかに且つ低コストで行うことが可能な固体撮像素子を提供する。

【解決手段】多数の光電変換素子1と、光電変換素子1から読み出された電荷をY方向に転送する複数の垂直転送チャネル2と、垂直転送チャネル2を転送されてきた電荷をX方向に転送する水平転送チャネル6とを有するCCD型の固体撮像素子であって、光電変換素子1と垂直転送チャネル2との間に形成される電荷読み出し領域TGを除く光電変換素子1の周囲に形成された素子分離領域3と、接地された遮光膜15とを、水平転送チャネル6近傍にて電気的に接続した。

(もっと読む)

撮像装置、撮像装置駆動方法及びプログラム

【課題】バッテリ残量が少なくなったとしても撮影に要する時間を長大させることなく撮影を継続することができる。

【解決手段】バッテリ残量Vbatが豊富な範囲を下回ったとき、CCD駆動速度については画像信号の読み出し時は低速(通常時の読み出し時と同じ速度)、掃き出し時も低速(通常時の掃き出し時よりも低い速度)とする。露光前のフィールドの時間間隔は通常時に比べて長くなる。画像信号読み出し中のフィールドの時間間隔のうち、掃き出し処理に要する時間は通常時に比べて長く、その掃き出し処理後の読み出し処理に要する時間は通常時と同じである。したがって、撮影処理に要するトータル時間を考えると、通常時に比べて掃き出し処理に要する時間が長くなる分だけ長くなる。また、撮影処理期間中、消費電流が格別高くなることはないため、バッテリ残量Vbatが実質ゼロとなる領域まで落ち込んでしまうことはない。

(もっと読む)

撮像素子

【課題】 信号電荷の増加に伴う静電容量の減少を防ぐことにより、撮像素子の電源電圧を低下させ、かつ高いダイナミックレンジの達成を図る。

【解決手段】 撮像素子の画素は、FD22、及びMOSキャパシタ27を有する。p型半導体である第2のウェル29bの表面の一部にn型半導体を接合させて、第2PN接合ダイオード32bを形成する。第2PN接合ダイオード32bがFD22を形成する。p型半導体である第4のウェル29dの表面の一部にn型半導体を接合させて、第7PN接合ダイオード32gを形成する。第7PN接合ダイオード32gのn型半導体層と第1の電極38とがMOSキャパシタ27を形成する。FD22と第1の電極38とを互いに接続する。

(もっと読む)

固体撮像装置

【課題】 確実に電子シャッタ動作、リセット動作を行うことができる固体撮像装置を提供する。

【解決手段】 光電変換部及び前記光電変換部で得られた電荷を転送する電荷転送部を有する固体撮像素子と、光電変換部で得られた電荷の移動を制御するための第1パルスを生成する第1パルス生成手段41と、第1パルスと同一のタイミングの第2パルスを生成する第2パルス生成手段42と、第1パルス及び第2パルスのいずれかと第1パルス及び第2パルスのいずれかとを加算し、得られたパルスを電子シャッタパルス又はリセットパルスとして固体撮像素子に出力する加算手段43とを備え、加算手段43はコンデンサ44とダイオード45とを有し、コンデンサ44の一端とダイオード45のカソードが接続され、コンデンサ44の他端に、加算の対象となる一方のパルスが入力され、ダイオード45のアノードに、加算の対象となる他方のパルスが入力される。

(もっと読む)

固体撮像素子と固体撮像装置、固体撮像素子の製造方法

【課題】 光電変換素子において発生した少数キャリアが、外部に容易に抜けるような構成の固体撮像装置を提供する。

【解決手段】 半導体基体4内に光電変換素子7が形成され、半導体基体4の表面側に設けられた絶縁層15内に配線層13が形成され、光電変換素子7に、半導体基体4の裏面側より光が照射される構成であり、光電変換素子7の周囲の半導体基体4内に半導体領域6が形成され、半導体基体4の裏面側より、半導体領域6内の少なくとも一部に導電材料層25が形成されている固体撮像素子1と、固体撮像素子1に対して電圧を印加する手段とを備えた固体撮像装置において、この手段から、導電材料層25に接地電位が印加されるように構成する。

(もっと読む)

1 - 14 / 14

[ Back to top ]