Fターム[4M119EE33]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | 接地線(GND) (28)

Fターム[4M119EE33]に分類される特許

1 - 20 / 28

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

【課題】ソース及びドレインにハーフメタルを用いたトランジスタを提供する。

【解決手段】一方のスピンに対し金属的スピンバンド構造を、他方のスピンに対し半導体的スピンバンド構造をとるハーフメタルからなり、スピン偏極した伝導キャリアを注入する強磁性ソースと、注入されたスピン偏極した伝導キャリアを受けるハーフメタルからなる強磁性ドレインと、強磁性ソースと強磁性ドレインとの間に設けられた半導体層と、強磁性ソースと半導体層との間及び強磁性ドレインと半導体層との間に設けられた金属層と、半導体層に対して形成されるゲート電極と、ソース及びドレインに対して形成された非磁性コンタクトと、を有し、金属層は、半導体層との界面において、ショットキー接合を形成し、非磁性コンタクトのフェルミエネルギーは、それぞれ強磁性ソース及び強磁性ドレインの半導体的スピンバンドのバンドギャップ中を横切るトランジスタ。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

薄膜磁性体記憶装置

【課題】書込まれる記憶データのレベルに依存せず磁気特性が対称な磁性体メモリセルを有する薄膜磁性体記憶装置を提供する。

【解決手段】トンネル磁気抵抗素子中の自由磁化層においては、静磁性結合に起因する固定磁化層との間の結合磁界ΔHpが、磁界容易軸(EA)に沿った方向に作用している。データ書込磁界H(WWL)は、自由磁化層の磁化困難軸(HA)と完全に平行に印加されるのではではなく、磁化困難軸HAとの間に所定角度αを成すように印加される。これにより、H(WWL)の磁化容易軸(EA)方向に沿った成分によって、一様な結合磁界ΔHpが相殺される。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

磁気メモリ素子、磁気メモリ、及びその製造方法

【課題】電流誘起磁壁移動現象を書き込み方法に採用したMRAMにおいて、磁壁移動の起こる磁性層に容易に磁壁を導入可能とする。

【解決手段】磁気メモリ素子70は、磁化自由層10と非磁性層20とリファレンス層30と磁化固定層群40と導電層50とを具備する。磁化自由層10は、垂直磁気異方性を有する強磁性体により構成され、第1磁化固定領域11aと、第2磁化固定領域11bと、第1磁化固定領域と第2磁化固定領域とに隣接した磁化自由領域12とを備える。第1磁化固定領域11a及び第2磁化固定領域11bは、互いに反平行方向に固定された磁化を有する。磁化固定層群40は、第1磁化固定領域11aと磁気的に結合した第1磁化固定層群40aと、第2磁化固定領域11bと磁気的に結合した第2磁化固定層群40bとを備える。導電層50は、第1磁化固定層群40aに隣接する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】スピン注入型の磁気ランダムアクセスメモリに関し、より小さいサイズのメモリセル選択トランジスタで効率的な書き込みが可能な磁気ランダムアクセスメモリを提供する。

【解決手段】ビット線24、接続導体層25及びMTJ素子30が形成された層間絶縁膜22上には、層間絶縁膜26が形成されている。層間絶縁膜26には、接続導体層25に接続されたプラグ27と、MTJ素子30に接続されたプラグ28とが埋め込まれている。層間絶縁膜26上には、プラグ27とプラグ28とを電気的に接続する局所内部配線29が形成されている。これにより、MTJ素子30のフリー層側は、プラグ28、局所内部配線29、プラグ27、接続導体層25、プラグ23、接続導体層21、及びプラグ19を介して、n型ドレイン領域16に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の生産性を向上させる。

【解決手段】シリコン基板1を覆う層間絶縁膜ILと、複数のメモリセルとを有する半導体装置であって、複数のメモリセルは、層間絶縁膜IL内に配置された記憶素子部mr1と、記憶素子部mr1に電気的に接続するようにして配置された下部電極BEおよび上部電極TEとを有する。下部電極BEと上部電極TEとは層間絶縁膜IL内において互いに交差するようにして配置され、その交差部に挟まれるようにして記憶素子部mr1が配置されている。記憶素子部mr1は、磁気抵抗メモリ、相変化メモリ、または、抵抗変化メモリからなる。

(もっと読む)

複合材の製造方法及び半導体装置の製造方法

【課題】大気中でも安定した複合材を容易に得ることができる複合材の製造方法及び半導体装置の製造方法を提供する。

【解決手段】基体1上に、複数の表面酸化微粒子2を堆積する。表面酸化微粒子2の直径は10nm以下であることが好ましく、例えば0.5nm〜5nm程度である。表面酸化微粒子2は、グラファイト層を形成する際の触媒として機能し得るコバルト等の強磁性体金属微粒子とこの表面を覆う酸化膜から構成されている。次いで、炉内に基体1及び表面酸化微粒子2を挿入し、炉内を高真空にして基体1を510℃程度まで昇温する。この結果、基体1及び表面酸化微粒子2に付着していた異物等が除去される。その後、炉内の雰囲気を炭化水素系ガス雰囲気にする。この結果、表面酸化微粒子2の表面に存在した酸化膜が還元され、更に、強磁性体金属微粒子の表面にグラファイトが析出し、グラファイト被覆微粒子3が強磁性体複合微粒子として得られる。

(もっと読む)

不揮発性半導体記憶装置

【課題】磁気ランダム・アクセス・メモリの書込に関連する回路のレイアウト面積を低減する。

【解決手段】可変磁気抵抗素子(VR)の磁化容易軸(EX)と直交する方向に書込ビット線(WBL0,WBL1)を配置し、書込データに応じて双方向に書込ビット線に電流を流す。一方、書込ビット線と交差するようにビット線(BL0−BL3)を配置し、書込データの論理値にかかわらず一定方向に電流を流す。書込ビット線へは、セルトランジスタ(CT)の耐圧よりも高い高電圧(VCC)から電流を供給する。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】ライトディジット線WDLは、データ書込電流の供給時に電源配線90と接続される。ライトディジット線WDLは、電源配線90側の末端付近に、MTJメモリセルの配置位置に対応する定常部分93と比較して断面積を増大ざせた強化部分95を有する。これにより、定常部分93ではMTJメモリセルの最小設計ルールに従った配線幅とすることによってメモリセルを高集積に配置できるとともに、電源配線90側の末端付近で金属原子の移動による配線幅の減少が生じても、この部分で電流密度が局所的に増大して動作信頼性に影響を与えることを防止できる。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】各ビット線BLの両端には、データ書込電流を流すためのビット線ドライバ50が配置される。各ビット線の一端は、データ読出時に選択メモリセルからの読出データを伝達するための読出選択ゲート65を介して、データバスRDB1またはRDB2と接続される。読出選択ゲート65は、メモリセルアレイ10に対して、ビット線ドライバ50よりも外側に配置される。これにより、データ書込電流の電流経路を短くして、その経路抵抗を低減できるので、データ書込電流の確保が容易になる。

(もっと読む)

記憶装置

【課題】スピン注入メモリ等の抵抗変化素子を用いた記憶装置において、抵抗変化素子の高集積化を可能とした記憶装置を提供する。

【解決手段】供給される電流の向きにより抵抗値が変化する複数の抵抗変化素子と、各抵抗変化素子への電流供給をオン−オフ制御する複数のアクセス用トランジスタと、複数の抵抗変化素子の一方端に接続したビット線と、複数の抵抗変化素子の他方端にそれぞれアクセス用トランジスタを介して接続したソース線と、各アクセス用トランジスタのゲートにそれぞれ接続した複数のワード線と、接地電位が印加されるグランド線と、オン状態となることによりビット線またはソース線とグランド線とを接続するスイッチ用トランジスタとを備えた記憶装置とし、抵抗変化素子へ電流供給する際に、スイッチ用トランジスタをオン状態にして、ビット線またはソース線を接地電位にする。

(もっと読む)

磁気抵抗効果素子、及び磁気ランダムアクセスメモリ

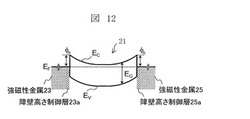

【課題】垂直磁化膜を用いた電流誘起磁壁移動現象を利用したMRAMについて、容易に磁壁を導入し、また磁壁のピニング力の過剰な増大を防ぎ、書き込み電流を充分に低減するための技術を提供する。

【解決手段】本発明の磁気抵抗効果素子は、垂直磁気異方性を有する強磁性体により構成される第1強磁性層10を具備する。第1強磁性層10は、第1の方向に固定された磁化を有する磁化固定領域11aと、前記第1の方向と反平行方向に固定された磁化を有する磁化固定領域11bと磁化固定領域11a、11bに接合された、反転可能な磁化を有する磁化自由領域12とを備える。磁化固定領域11aは、その上面11aTが磁化自由領域12の上面12Tよりも基板垂直方向において高い位置に形成され、磁化固定領域11aの下面11aBは、磁化自由領域12の下面12Bよりも基板垂直方向において低い位置に形成される。

(もっと読む)

磁気記憶装置

【課題】書き込み特性の安定した磁気記憶装置を提供する。

【解決手段】磁気記憶装置は記録層3を有する。記録層3の平面形状は、磁化容易軸91に沿った一の直線63上で磁化容易軸91の方向における最大の長さLを有し、磁化容易軸91と垂直な方向に最大の長さLの半分より小さい長さWに渡って位置し、一の直線63の一方側および他方側のそれぞれにおいて、磁化容易軸91と垂直な方向に長さaに渡って位置する第1の部分3aと、磁化容易軸91と垂直な方向に長さaより小さい長さbに渡って位置する第2の部分3bとを有している。第1の部分3aの外縁は、外縁の外側に向かって凸の滑らかな曲線のみからなる。

(もっと読む)

半導体装置

【課題】読み出し動作の速度低下を防ぎ、電源の低電圧化を図り、かつデータ読み出しを正確に行なうことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の差動アンプAMP0の第1入力端子と第1の定電圧トランジスタTRC0との間に直列接続された第1の選択トランジスタTRW0Aと、第1の差動アンプAMP0の第1入力端子と第2の定電圧トランジスタTRC1との間に直列接続された第2の選択トランジスタTRW0Bとを備え、第1の定電圧トランジスタTRC0は、第1の可変抵抗素子S0と第1の選択トランジスタTRW0Aとの間に接続され、第2の定電圧トランジスタTRC1は、第2の可変抵抗素子S2と第2の選択トランジスタTRW0Bとの間に接続されている。

(もっと読む)

磁気抵抗ランダムアクセスメモリ(MagnetoresistiveRandomAccessMemory:MRAM)ビットセルのアレイ・ストラクチャル・デザイン(arraystructuraldesign)

スピン・トランスファ・トルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルが開示される。前記ビットセルは、第1の面内に形成されたソース線と、第2の面内に形成されたビット線とを含む。ビット線は、前記ソース線の長手方向軸に対して平行である長手方向軸を有し、かつ、前記ソース線は少なくとも前記ビット線の一部にオーバーラップする。  (もっと読む)

(もっと読む)

半導体装置

【課題】簡易な構成で磁気抵抗素子のデータ書き換え特性の評価を正確に行なうことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の電圧が供給される第1端と、第2端とを有し、データ書き込み時、磁気抵抗素子Sにデータを書き込むための書き込み電流が流れ、書き込み電流の方向が書き込みデータの論理値に依存しない書き込み電流線DLと、書き込み電流線DLの第2端に結合される第1導通電極と、第2の電圧が供給される第2導通電極とを有し、データ書き込み時、書き込み電流線DLに書き込み電流を流すことにより、磁気抵抗素子Sの磁化に作用する磁場を発生するトランジスタTRDと、第1の電圧が供給される第1のパッドPD1と、第2の電圧が供給される第2のパッドPD4と、半導体装置101が備える他の回路に第3の電圧を供給するための第3のパッドPD2,PD3とを備える。

(もっと読む)

積層されたNAND型抵抗性メモリセルストリングを含む不揮発性メモリ素子及びその製造方法

【課題】積層されたNAND型抵抗性メモリセルストリングを含む不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】NAND型抵抗性メモリセルストリングSTR1,STR2は、ビットラインBL及びビットラインBLに直列接続された複数個の抵抗性メモリセルCL1,CL2,CL3を含み、複数個の抵抗性メモリセルCL1,CL2,CL3のそれぞれは、第1ノードN1、第2ノードN2及び第3ノードN3、第1ノードN1と第2ノードN2との間に接続されたヒータH1、H2、H3、第2ノードN2と第3ノードN3との間に接続された可変抵抗体R1、R2、R3、第1ノードN1に接続された第1端子及び第3ノードN3に接続された第2端子を有するスイッチング素子SW1、SW2、SW3とを含む。

(もっと読む)

1 - 20 / 28

[ Back to top ]