Fターム[5B022BA05]の内容

Fターム[5B022BA05]に分類される特許

1 - 2 / 2

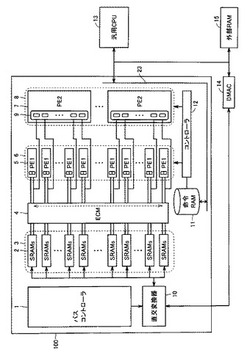

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

ビット長検出器、ビット長検出方法及びビット長検出プログラム

【課題】入力データのビット数が大きく変動する場合にもビット数を高速に検出すること。

【解決手段】入力データビット長検出部120は、最初にRビットを検査対象ビットブロックとし、基準位置からRビットを二等分して上位半分のビットブロックと下位半分のビットブロックとに分けたビット分木初期位置まで前記上位半分のビットブロックを選択して右シフトし、右シフトの結果に基づいて当該上位半分のビットブロックと前記下位半分のビットブロックのいずれかを次の検査対象ビットブロックとして選択し、当該選択された次の検査対象ビットブロックの上位半分のビットブロックを選択して右シフトする動作を繰り返して、ビット分木終了位置まで右シフトして最終シフトビット数累積値を求め、当該最終シフトビット数累積値と前記動作において最後に検査対象ビットブロックとして選択されたビットのデータの値とを加算して入力データのビット長を検出する。

(もっと読む)

1 - 2 / 2

[ Back to top ]