Fターム[5B045GG15]の内容

マルチプロセッサ (2,696) | プログラム、命令の実行処理 (212) | 並列処理 (89) | MIMD (5)

Fターム[5B045GG15]に分類される特許

1 - 5 / 5

画像音声信号処理装置及びそれを用いた電子機器

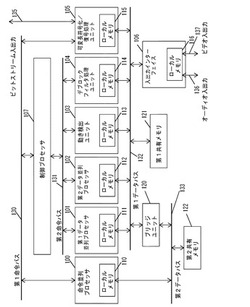

【課題】 MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供する。

【解決手段】 信号処理装置は、命令並列プロセッサ100、第1データ並列プロセッサ101、第2データ並列プロセッサ102、及び、専用ハードウェアである動き検出ユニット103とデブロックフィルタ処理ユニット104と可変長符号化/復号処理ユニット105とを備える。この構成により、処理量の多い画像圧縮伸張アルゴリズムの信号処理において、ソフトウェアとハードウェアで負荷が分散され高い処理能力と柔軟性を実現した信号処理装置、及びそれを用いた電子機器を提供出来る。

(もっと読む)

画像出力装置および3次元画像表示システム

【課題】マルチコアプロセッサを用いて複数の画像データを効率的に並列処理して出力可能にする。

【解決手段】複数の画像メモリ51〜54と、マルチコアプロセッサ21内の複数のコア31〜34とを、バス25を介して1対1に対応させる。そして、複数のコア31〜34によって画像処理された複数の画像データを、バス25を介して複数の画像メモリ51〜54に並列的に格納する。複数の画像メモリ51〜54に格納された複数の画像データは、複数の出力I/F55〜58によって並列的に出力される。すなわち、ビデオカードのGPUを用いることなく、マルチコアプロセッサ21によって直接的に画像処理された複数の画像データを、複数の画像メモリ51〜54および複数の出力I/F55〜58を介して並列的に出力する。これにより、マルチコアプロセッサ21が有するコアの数だけ並列的に画像処理を行って並列的な画像出力が可能となる。

(もっと読む)

自律または共通制御されるPEアレイを有するシステムのためのデータ転送ネットワークおよび制御装置

SIMD/MIMDデュアルモードのアーキテクチャプロセッサは、共通制御される第1のプロセッシングエレメント(PE)群と、自律制御される第2のプロセッシングエレメント群と、前記第1、第2のPE群を順次接続するパイプラインネットワークと、を備える。アクセスコントローラは、前記第1、第2のPE群の各PEにそれぞれ接続されたアクセス制御線を有し、前記各PEと前記パイプラインネットワークとの間のデータアクセスタイミングを制御する。各PEは、SIMD/MIMDデュアルモードのアーキテクチャプロセッサのように自律制御または共通制御することが可能である。配線エリア要件を緩和する。  (もっと読む)

(もっと読む)

情報処理システムおよび情報処理方法

分散メモリ型において、単一命令により種々のメモリに記憶された配列中の要素を入出力し、処理と通信を統合する。隣接するPMM12の間には、一方から他方にパケットを伝達する第1のパケット伝送路14、および、他方から一方にパケットを伝達する第2のパケット伝送路16を備える。各PMMは、各々が項目と当該項目に属する項目値とを含むレコードの配列として表される表形式データを表現するための、特定の項目に属する項目値に対応した項目値番号の順に当該項目値が格納されている値リスト、および、一意的な順序集合配列の順に、当該項目値番号を指示するためのポインタ値が格納されたポインタ配列からなる情報ブロックを保持し、各メモリにて保持された情報ブロックの集合体により、グローバルな情報ブロックが形成される。  (もっと読む)

(もっと読む)

クラスタ化されたILPプロセッサ

本発明の基本概念は、待ち時間が非一様の完全接続クラスタ間ネットワークに基づくクラスタ化ILPプロセッサを提供することである。クラスタ化命令レベル並列処理プロセッサが提供される。前記プロセッサは、少なくとも1つのレジスタ・ファイル(RF)および少なくとも1つの機能単位(FU)をそれぞれ有する複数のクラスタ(C1〜C6)を有し、前記クラスタ(C1〜C6)が互いに完全に接続され、前記クラスタ(C1〜C6)間の接続の待ち時間が、前記クラスタ(C1〜C6)間の距離に依存する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]