Fターム[5B060CB02]の内容

Fターム[5B060CB02]の下位に属するFターム

論理演算を伴うロード/ストア (24)

ロード/ストアによるメモリ内容の修正 (16)

Fターム[5B060CB02]に分類される特許

1 - 11 / 11

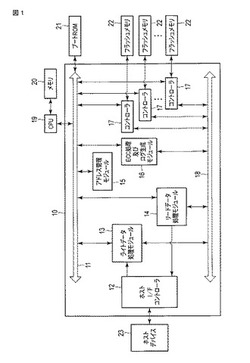

データ記憶装置、メモリ制御装置及び方法

【課題】フラッシュメモリに書き込み要求のデータを書き込むための処理効率を向上できるデータ記憶装置を提供する。

【解決手段】書き込みデータ処理モジュール13は、ホスト装置23からの書き込みデータが所定サイズ未満の場合に、フラッシュメモリ22から書き込みデータと同一のアドレスで管理されている所定サイズのデータを読み出し、バッファメモリ内で書き込みデータを含む所定サイズのデータをセットするためのマージ処理を実行する。さらに、書き込みデータ処理モジュール13は、フラッシュメモリ22からのデータの読み出し時または読み出し完了時に、バッファメモリ内での旧書き込みデータと同一のアドレスで管理される新書き込みデータが存在した場合に、新書き込みデータをマージ対象データとしてバッファメモリ内でのマージ処理を実行する。

(もっと読む)

インターフェース回路およびデータ転送方法

【課題】CPUとメモリとの間のデータ転送のスループットを向上させることが可能なインターフェース回路を提供することである。

【解決手段】本発明にかかるインターフェース回路3は、リードアドレス52を出力するリードアドレス生成部12と、メモリ2から読み出されたリードデータ54を正転して出力するかまたは反転して出力するかを示す反転情報が予め格納されており、リードアドレス52に対応したリードデータの反転情報53を出力する反転情報生成部13と、反転情報生成部13から出力された現在の反転情報53と一つ前の反転信号55と、に基づき反転信号を出力する演算回路14と、演算回路14から出力された反転信号56に応じて、リードデータ54を正転または反転して出力するデータ正転/反転部15と、を備える。

(もっと読む)

コンピュータシステム及び揮発性メモリ装置

【課題】DRAMなどの揮発性メモリ装置に係わり、リフレッシュ時に必要な消費電力の低減を実現できる技術を提供する。

【解決手段】本コンピュータシステム1は、DRAM2とCPU4を含んで成り、例えばCPU4側にデータ反転制御回路100を備える。データ反転制御回路100は、DRAM2への書き込み時(a)のデータにおける所定幅の書込データ単位ごとに、値“1”の数が過半数かどうかを判定し、過半数である場合は、値“1”/“0”を反転処理する。またデータ反転制御回路100は、DRAM2からの読み出し時(b)のデータにおける所定幅の読出データ単位ごとに、上記反転状態の値“1”/“0”を反転処理して復元し、読み出しデータとする。上記構成により、DRAM2におけるリフレッシュ動作の対象となる値“1”が記憶されるメモリセルの数を少なくする。

(もっと読む)

携帯可能電子装置

【課題】動作プログラムを擬似的に修正可能な携帯可能電子装置を提供すること。

【解決手段】携帯可能電子装置は、アドレスにより管理された第1の記憶領域により構成されたデータ書き換え不能な第1の記憶手段と、アドレスにより管理された第2の記憶領域により構成されたデータ書き換え可能な第2の記憶手段と、前記第1の記憶領域の監視対象アドレスと前記第2の記憶領域のジャンプ先アドレスとを対応付けたアドレス管理情報を管理するアドレス管理手段と、アクセス対象のアドレスをカウントするカウント手段と、前記前記カウント手段による前記監視対象アドレスのカウントに対応して前記カウント手段に前記ジャンプ先アドレスを設定し、前記カウント手段に設定された前記ジャンプ先アドレスに従って、前記ジャンプ先アドレスに記憶されたデータを読み出すデータ処理手段と、を備えている。

(もっと読む)

メモリストレージ装置及びその制御方法

【課題】メモリの消去回数の平均化の効率を向上させる。

【解決手段】メモリストレージ装置の制御方法は、ホストにおいて更新データを前記メモリストレージ装置内への書き込みに適用し、メモリストレージ装置は、前記更新データを格納するための複数の物理ブロックのストレージスペースを提供する。前記制御方法は、先ず、書き込もうとする更新データはホットデータであるか否かを判断し、最後に、判断結果に基づいてホットデータではない、更新の少ないデータを消去回数の高い物理ブロック内に搬送する。

(もっと読む)

フラッシュ・メモリにおけるソフト・デマッピングおよびセル間干渉軽減のための方法および装置

フラッシュ・メモリにおけるソフト・デマッピングおよびセル間干渉軽減のための方法および装置が提供される。一変種において、1セル当り少なくとも2つのデータ・レベル、sを格納することができるフラッシュ・メモリ・デバイスにおけるターゲット・セルが、フラッシュ・メモリにおける少なくとも1つのターゲット・セルに関する測定された読み取り値、rを獲得すること、フラッシュ・メモリにおける少なくとも1つのアグレッサ・セルに関して格納されたデータを表す値、hを獲得すること、フラッシュ・メモリの少なくとも一部分の中に格納された値のパターンに基づいて、フラッシュ・メモリにおける少なくとも1つのターゲット・セル上の、1つまたは複数のアグレッサ・セルのパターン依存の妨害を備える1つまたは複数の確率密度関数を選択すること、測定された読み取り値、rに基づいて、選択された少なくとも1つの確率密度関数を評価すること、および評価するステップの結果に基づいて、1つまたは複数の対数尤度比を計算することによって読み取られる。  (もっと読む)

(もっと読む)

符号化書き込みマスキング

【課題】 帯域幅が十分に確保されたメモリシステムを提供する。

【解決手段】 メモリコントローラと、メモリコントローラに結合されたメモリ装置とを有するメモリシステム。メモリコントローラは、書き込みデータ値をメモリ装置に出力する。メモリ装置は、メモリコントローラから書き込みデータ値を受信して、書き込みデータ値をマスクキー値と比較する。書き込みデータ値がマスクキー値にマッチする場合、メモリ装置は書き込みデータ値を記憶しない。書き込みデータ値がマスクキー値にマッチしない場合、メモリ装置は書き込みデータ値を記憶する。

(もっと読む)

メモリアクセス制御回路及びその方法

【課題】 データの切り替えによるノイズの発生量が多くなり、このようなノイズによる動作マージンの低減が問題となる。

【解決手段】 メモリデバイス3100への書込みデータが特定のパターンを含む場合にその特定のパターンを、反転するビットの数がより少ない省ノイズデータに変換し(3034)、その変換内容を示すコード(3032)とともに、その変換されたデータをメモリデバイス3100に出力する。メモリデバイス3100からのデータの読出し時、データの変換内容を示すコードとともに、当該データを読み出し、そのコードが、データが変換されていることを表している場合に特定のパターンを選択し、コードがデータが変換されていることを表していない場合に、入力したデータを読出しデータとして選択する(3022)。

(もっと読む)

メモリ制御回路及びメモリ制御方法

【課題】メモリチップ、メモリモジュールの書き込み、読み出し時のデータ切り替えに伴うノイズを削減できるようにすることを目的としている。

【解決手段】複数個のバーストから成るライトデータをメモリに書き込む際に、前記バーストの順番を並べ替えてn種類のライトデータを生成するとともに、前記n種類のライトデータの中から、メモリに書き込む際のデータ切り替え回数が前記バーストの順番を並べ替える前よりも少ないライトデータを選択し、更に選択されたライトデータのバースト並び順を冗長ビットにエンコードするようにして、前記選択されたライトデータと、前記エンコードされた冗長ビットとを前記メモリに書き込むようにすることにより、メモリリード、ライト時のデータ切り替え回数をできる限り低減できるようにする。

(もっと読む)

データ処理装置装置およびデータ処理方法

【課題】 JPEG圧縮を行う場合には圧縮画像データのサイズが原画像データのサイズよりも大きくなってしまう場合や、一部分に複雑なデータがあった場合には、まだ読み出していない原画像データの領域に圧縮画像データを書き込んでしまう場合がある。

【解決手段】 同一メモリ上に読み出し領域と書き込み領域を設定し、読み出し領域から読み出したデータを書き込み領域に書き込むデータ処理装置であって、書き込み領域の先頭アドレスを読み出し領域の先頭アドレスよりも前に設定する書き込み領域設定手段と、設定した書き込み領域に書き込みができなくなったときの読み出し領域の読み出しアドレスを取得する読み出しアドレス取得手段と、取得した読み出しアドレスに基づいて書き込み領域を再設定する書き込み領域再設定手段とを有する。

(もっと読む)

共有データ処理回路、情報処理装置、情報処理システム、共有データ処理方法、共有データ処理プログラム

【課題】 自系のメモリ装置内のデータと他系のメモリ装置内のデータとの相違の詳細(差分)を生成する。

【解決手段】 主記憶制御部102は、プロセッサ101からの共有アドレスを伴う差分要求により、主記憶部103から読み出しデータを読み出す。共有メモリ通信制御部104は、系間通信手段300を介して主記憶読み出し要求を情報処理装置200へ出力する。情報処理装置200では、主記憶読み出し要求により、主記憶部203から主記憶制御部202共有メモリ通信制御部204、を通じて読み出しデータを読み出し情報処理装置100へ出力する。主記憶制御部102は、共有メモリ通信制御部104を通じて読み出しデータを入力し主記憶部103からの読み出しデータとの差分を生成し、プロセッサ101に出力する。

(もっと読む)

1 - 11 / 11

[ Back to top ]