Fターム[5B079AA08]の内容

Fターム[5B079AA08]に分類される特許

1 - 4 / 4

パケット受信装置

【課題】休止状態にあるホストプロセッサを頻繁に起動しないことにより、休止状態から稼働状態に遷移する際の時間的オーバヘッドを軽減するとともに、オーバヘッド時間に浪費する電力を抑制し、通信性能の向上を図ること。

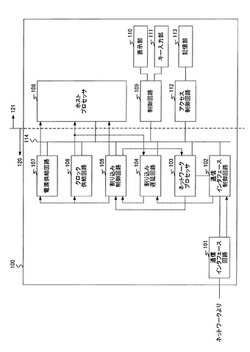

【解決手段】通信インタフェース回路101は、受信信号からパケットデータを抽出する。通信インタフェース制御回路102は、割り込み信号を生成して出力する。ネットワークプロセッサ103は、パケットデータを解析して、解析結果に基づいて、パケットデータをホストプロセッサ108に転送するか否かを判定する。割り込み制御回路105は、ネットワークプロセッサ103から割り込み信号を受け取った際に、ホストプロセッサ108を起動させる。ホストプロセッサ108は、電源及びクロックの供給を受けて起動し、割り込み信号を受けてパケットデータの受信処理を実行する。

(もっと読む)

クロック非同期切替装置およびノイズキャンセル回路ならびにノイズキャンセル方法およびプログラム

【課題】クロックフィールドをサンプリングするサンプリングクロックがACTIVE系とSTANDBY系とで同期が取れていない場合でも、系切替時におけるハザードノイズの発生を防止することが可能なクロック非同期切替装置の提供。

【解決手段】 カウンタ回路24のEX・OR回路28で入力クロックc5bのレベル変化が検出されると、カウントアップ部29はカウントを開始する。そして、所定カウント値N以下で次のレベル変化が検出されると、最初のレベル変化で検出されたパルスはハザードノイズと判定し、カウント値を0にクリアする。ノイズマスク回路35はカウント値が0である間入力クロックc5bの出力をマスクする。

(もっと読む)

DLL回路

【課題】第1のクロック出力をLPFで平滑化した値と、第1のクロック信号を遅延した第2のクロック信号の位相比較を行い、位相比較器の出力結果であるUP/DN信号のエッジを1/2に分周したクロック信号の出力をLPFで平滑化した値を、オペアンプを用いた負帰還制御で調整するDLL回路を提供する。

【解決手段】第1のクロック信号PH0をLPF20で平滑化した第1の電圧値と、位相比較した出力信号のエッジを検出し、かつその検出結果を論理和出力した信号を1/2に分周した信号をLPF21で平滑化した第2の電圧値と、をオペアンプ22に入力し、このオペアンプ22の出力電圧で、第1と第2の平滑化した電圧が同じになるように、前記充/放電電流を調整する。

(もっと読む)

コンピューティング・システムにおける電力をセーブするためにデューティ・サイクルを調整する方法と装置

コンピューティング・システムにおける電力をセーブするためにデューティ・サイクルを調整する方法とシステムであり、システムは、アクティブ・モードおよびスリープ・モードを有するネットワーク・インターフェース・カード(NIC)有して、NICは、電力消費量を最小にすることに少なくとも一部基づいて、能動時間をスリープ・タイムにするデューティ・サイクルを調整する調整要素に接続される。 (もっと読む)

1 - 4 / 4

[ Back to top ]