Fターム[5C024HX38]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | 発振回路 (65) | PLL (20)

Fターム[5C024HX38]に分類される特許

1 - 20 / 20

平面型X線センサ

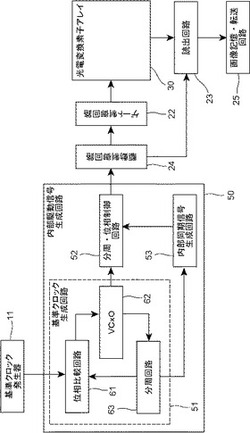

【課題】内部駆動タイミングと外部基準クロックとを整合させる。

【解決手段】X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサの内部駆動信号を生成する内部駆動信号生成回路50に、PLL構成の基準クロック生成回路51を備える。基準クロック生成回路51は、電圧制御発振器62と分周回路63と位相比較回路61とを備える。電圧制御発振器62は、たとえば水晶発振器を用いて、内部基準クロックを生成する。分周回路63は、内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する。位相比較回路61は、外部基準クロックと前記分周クロックとの位相を比較してその位相差を電圧制御発振器62に入力する。

(もっと読む)

撮像装置および撮像システム

【課題】 従来から知られていた撮像装置では、各信号処理回路に対してバッファ素子を設けているため、信号処理回路の数に比例してバッファ素子の数が増大する。また、複数の信号処理回路を1つのグループとして、各グループ内で駆動信号が遅延して供給されるので、動作タイミングのマージンを長く設定する必要が生じる。つまり、動作の高速化が図りにくい。

【解決手段】 互いに直列に接続された第1のバッファ回路と、第1のバッファ回路に対して並列に接続される第2のバッファ回路を設け、1個の第2のバッファ回路で複数の前記信号処理部に前記駆動信号を供給する。

(もっと読む)

固体撮像素子およびその駆動方法、カメラシステム

【課題】レート変換のためにバッファが不要で、低回路規模化、低消費電力化を図ることが可能な固体撮像素子およびその駆動方法、カメラシステムを提供する。

【解決手段】レート変換情報に応じて、カラム処理部で処理されたデータのレート変換制御を行うレート変換制御部を有し、レート変換制御部は、第2の周波数の第2のクロックである基準クロックを基に、第1のクロックを生成してカラム処理部に供給する第1のレート変換器と、第2の周波数の第2のクロックである基準クロックを基に、データレートに応じて変化する第3の周波数の第3のクロックを生成する第2のレート変換器と、カラム処理部で処理されたデータのレートを加算処理を含んだ処理により変換し、変換後または変換前のデータを第2のデータとして出力するデータレート変換部と、第3のクロックに同期してデータレート変換部による第2のデータを出力するデータ出力部と、を含む。

(もっと読む)

光電変換装置および撮像システム

【課題】 従来の技術では、消費電力の増大や画質の低下を抑制しつつ、読み出しの高速化を実現することが困難であった。

【解決手段】 画素アレイの列に対応して設けられた、画素から出力された信号をデジタル信号に変換する複数のA/D変換部を少なくとも含む信号処理部と、2以上の出力端子を有し、出力端子の各々に対応して設けられた複数の出力ブロックを含む出力部と、同期信号を出力する同期信号生成部と、を含み、互いに隣接するまたは1列おきの複数の列の信号処理部をブロックとして、出力ブロックは、前記ブロックに属する複数の信号処理部から出力された信号を出力し、同期信号に同期して、出力ブロックから出力される信号に対して同期コードを付加する同期コード付加部をさらに有する。

(もっと読む)

固体撮像素子およびカメラシステム

【課題】VCOの性能に左右されず、高速にA/D変換を実行できることはもとより、PLLの入出力特性のばらつきを抑制することができ、ゲイン性のある縦筋の発生を防止することが可能な固体撮像素子およびカメラシステムを提供する。

【解決手段】読み出し部は、読み出し信号の電圧に応じた周波数のクロック信号を生成するVCO1411と、VCOが生成したクロック信号をカウントするプリカウンタ1412と、プリカウンタの出力をカウントするカウンタ1416と、を含み、第1の期間にはプリカウンタおよびカウンタのカウント動作は第1の方向に動作し、第2の期間にはプリカウンタおよびカウンタのカウント動作は逆の第2の方向に動作し、ダミー画素のゲートに第1の期間と第2の期間で異なるレベルの信号を印加し、カウンタに保持された値をVCOの入力電圧と出力周波数の比であるKv値として出力する第1の処理を行う。

(もっと読む)

カラムA/D変換器、カラムA/D変換方法、固体撮像素子およびカメラシステム

【課題】消費電力を大幅に低減することが可能なカラムA/D変換器、カラムA/D変換方法、固体撮像素子、およびカメラシステムを提供する。

【解決手段】コードカウンタ200は、基準クロックPLLCKに基づくカウント処理により複数ビットのコードを生成し、複数のカラム処理部300の各々は、時間とともに電圧値が線形に変化するランプ波形の参照電圧と入力電圧とを比較する複数の比較器310と、比較器の出力信号が反転したことをトリガとして、反転した比較器の出力信号に応答してコードカウンタで生成された複数ビットを下位ビットとしてそれぞれラッチする下位ビットラッチ部320と、下位ビットラッチ部の最上位のラッチデータをキャリーとして順次にカウントする上位ビットカウンタ330と、を含む。

(もっと読む)

画像撮像装置

【課題】NTSC方式のフレーム周波数から外したフレーム周波数で撮像素子から画像データを取り込み、フレームメモリにプログレッシブで書込み、インタレースで読み出す撮像装置におけるインタレース特有のコムノイズの発生を防止、また、実装するクロック発振器はNTSC方式対応の発振器のみとして、低コストな撮像装置を提供する。

【解決手段】フレームメモリ105を少なくとも3つの領域に分ける。制御部10は、各領域を書込み領域・読出し領域として、その役割を順次切り替えるようにし、ある領域からの読出し終了時に、次に読出す領域への書込みが完了しているか確認して、読出し領域の切替えを行う。撮像素子101は、NTSC方式対応の発振器107のクロックで動作し、垂直方向のブランキング期間乃至水平方向のブランキング期間を変更することで、NTSC方式のフレーム周波数から外れたフレーム周波数で画像データを出力する。

(もっと読む)

固体撮像装置

【課題】画素が出力する信号を増幅する機能を容易な回路構成で実現することができる。

【解決手段】周波数変換部101は、撮像部2が出力する信号の大きさに応じて入力信号と出力信号との遅延時間が変化する反転回路を複数個リング状に連結した連結回路と、反転回路の出力端子と反転回路とは隣接していない他の反転回路の入力端子との間に接続した1つまたは複数のスイッチ素子とを備え、連結回路に応じた周波数を有するクロック信号を生成する。制御部20は、周波数変換部101が備えるスイッチ素子の開閉を制御する。カウント部103は、周波数変換部が生成したクロック信号を計数する。

(もっと読む)

撮像装置及び当該装置における信号処理方法

【課題】 撮像センサから並列に出力される複数の画素信号を並行して処理する。

【解決手段】 複数の画素信号のそれぞれに対応して設けられた複数のパラレルシリアル変換器109,110のそれぞれに入力される画素信号に、水平同期信号に同期した同期コードを付加し、これら複数のパラレルシリアル変換器により、第1のクロック信号に同期してパラレルの画素信号をシリアルの画素信号に変換する。こうして変換されたシリアルの画素信号から同期コードを検出し、複数のシリアルパラレル変換器112,114により、複数のシリアルの画素信号をパラレルの画素信号に変換する。こうして複数のシリアルパラレル変換器112,114から出力される複数のパラレルの画素信号の同期を調整して(116)、複数の画素信号に対応する多値画像データを出力する。

(もっと読む)

タイミング信号発生器及びそれを備えた画像読取装置

【課題】基準クロックに基づいて所定の周期に同期したタイミング信号を発生するTG(Timing Generator)を仕様の異なるイメージセンサに使用可能にする。

【解決手段】TG25には、水晶振動子27の出力が、周波数拡散をかけるSSCG26を介して入力される。入力されたクロックをPLL回路28により逓倍し、画素周波数と同じ周波数の画素クロック(pixck)を生成する。画素クロックをDLL回路29に供給し、画素クロック周期を60分割した多層クロックを生成する。クロック生成部30にて、多層クロックから必要な位相を選択することで、タイミング信号を生成する。タイミング信号の位相、パルス幅、出力期間等の調整はCPU I/F34を介したレジスタ設定で行う。

(もっと読む)

固体撮像装置、駆動制御方法、および撮像装置

【課題】アナログの画像信号をAD変換する際の量子化誤差を低減することができるようにする。

【解決手段】カウンタ4は、DUTY調整回路33を介して供給されるPLL回路5からのクロック信号に基づいて、アナログの画素信号をデジタルの画素データに変換する。DUTY計測部32は、画像データのLSBから、クロック信号のDUTY比を計測する。DUTY調整回路33は、DUTY計測部32により計測されたクロック信号のDUTY比に基づいて、DAC2およびカウンタ4に供給されるクロック信号が50%となるように、出力されるクロック信号のDUTY比を調整する。本発明は、例えば、列並列AD変換方式のCMOSイメージセンサに適用できる。

(もっと読む)

半導体装置、固体撮像素子、およびカメラシステム

【課題】寄生インダクタンスとバイパスキャパシタ2のキャパシタンスに起因する発振周波数を変更可能で、ノイズの増幅を防止でき、クロックのジッタを抑えることが可能な半導体装置、固体撮像素子、およびカメラシステムを提供する。

【解決手段】パッケージのインダクタンスLとバイパスキャパシタC20のキャパシタンスCとにより、2π√LCで与えられる共振周波数fを、キャパシタンスCを可変とすることにより、調整可能に構成された調整回路21を有する。

(もっと読む)

撮像装置及びその制御方法

【課題】撮像素子及び信号発生手段間の端子数の削減、伝送特性の向上、信号発生手段からの放射ノイズの低減等を可能とした撮像装置及びその制御方法を提供する。

【解決手段】デジタルカメラは、撮像素子101、タイミング信号発生回路104を備える。撮像素子101のLVDSレシーバ1011、S/P変換ブロック1012、撮像ブロック1013を同一の半導体チップ上に形成する。タイミング信号発生回路104のタイミングジェネレータ部1041、P/S変換ブロック1042、LVDSドライバ1043、PLL部1044を同一の半導体チップ上に形成する。タイミング信号発生回路104は、複数の制御信号のうち動作周波数が高速な制御信号よりも更に高速な周波数のクロックを生成し、クロックにより複数の制御信号を多重化しシリアル化し、低電圧差動伝送方式で撮像素子101に転送する。撮像素子101は、多重化信号を受信し、元の制御信号に復号化する。

(もっと読む)

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

固体撮像装置及び撮像装置

【課題】装置の起動時や急激な負荷変動時などに適正な電流供給を行い、起動動作の高速化や負荷変動の抑制を図る。

【解決手段】チャージポンプ回路の出力電圧を検知し、チャージポンプ回路のスイッチング周波数を可変制御することにより、電流供給能力を制御して、出力電圧の変動を吸収する。これにより、例えば起動時の電圧変化を短時間に収束し、起動後の動作を高速化したり、急激な負荷変動を最小にして動作の安定化を図る。したがって、起動の高速化により固体撮像装置を積極的に休止状態とし、機器の低消費電力化が実現できる。また、瞬間的な電流の供給先としては、例えば外付けの容量等となるが、電流供給能力を高めることで、外付けの容量に素早く電荷をチャージでき、結果として、より小さな容量を選択することも可能になり、コスト並びにレイアウトの面で改善が期待できる。

(もっと読む)

イメージセンサテスタ

【課題】ジッタの少ないクロック回路をパフォーマンスボード上に搭載することで、撮像試験における画像のノイズを低減し、なおかつユーザーが必要とする周波数のクロックを供給することを目的とする。

【解決手段】複数の周波数のクロックを用い、パフォーマンスボードおよびプローブカードを介して被測定デバイスの撮像試験を行うイメージセンサテスタにおいて、前記複数の周波数のクロック発生回路を前記パフォーマンスボード又はプローブカード上に配置した。

(もっと読む)

固体撮像装置

【課題】クロック周波数を上げたり、読みだし速度を遅くしたりすることなく、必要な範囲で高ビット精度の出力を得ることを可能とする。

【解決手段】入射光量を電気信号に変換する複数の画素12を有し、該画素12から得られるアナログ信号をデジタル信号に変換する複数のアナログ−デジタル変換装置(列並列ADCブロック15)を有する固体撮像装置において、前記アナログ−デジタル変換装置は、時間変化する参照電圧と画素から得られるアナログ信号とを比較するもので異なった参照電圧が入力される複数の比較器21,22と、前記比較器21,22における比較完了までの時間をカウントして、その結果を保持するもので、異なったカウント数を有するカウンタ23,24とから構成されていることを特徴とする。

(もっと読む)

タイミング発生回路

【課題】基準クロックを変更しても、高精度のタイミングクロックを即座に生成可能なタイミング発生回路を提供する。

【解決手段】遅延装置20に含まれる遅延回路21の入出力間に接続される遅延素子の数を変更可能にしておき、基準クロックck2の切り替えを指示する信号freqに応じてこの数を変更することで、遅延装置20全体の遅延時間を瞬時に変更する。

(もっと読む)

パルス生成回路、撮像装置及びカメラ

【課題】 固体撮像素子を駆動するパルスである周期的パルス及び非周期的パルスの位相関係を、温度、電源電圧、素子特性などの変化やばらつきに影響されることなく一定に保つことができるパルス生成回路、撮像装置及びカメラを提供する。

【解決手段】 位相制御回路3は、クロック信号CLKI_1の位相に応じた位相となるよう第2のクロック信号の位相制御を行う。第1のタイミング信号発生回路2は、位相制御回路3により位相制御された第2のクロック信号を基に周期的な波形のパルスを生成する。第2のタイミング信号発生回路4は、クロック信号CLKI_2〜4に同期した非周期的なパルスを生成する。クロック分配回路1は、入力されたクロック信号CLKを基に、第1のタイミング信号発生回路2及び第2のタイミング信号発生回路4に相対的な遅延差なくクロック信号CLKI_1〜4を分配する。

(もっと読む)

CCD制御信号生成装置、および画像読取装置

【課題】 EMI対策を安価に行え、高画質な画像データを得られるCCD制御信号生成装置、およびこのCCD制御信号生成装置を備える画像読取装置を提供する。

【解決手段】 基本クロックを発生するPLL22と、基本クロックを入力とし、基本クロックの一定でない所定クロック数ごとに内部基準クロックを発生する内部基準クロック生成回路23と、基本クロックと内部基準クロックとを入力とし、内部基準クロックが入力されてから、基本クロックの一定の所定クロック数後に、電荷結合素子の駆動タイミングを与えるCCDクロックを発生するCCDクロック生成回路25と、基本クロックとCCDクロックとを入力とし、CCDクロックが入力されてから、基本クロックの一定の所定クロック数後に、画像データのサンプリング期間を与えるサンプルホールド信号を発生するサンプルホールド信号生成回路26とをCCD制御信号生成回路2に備える。

(もっと読む)

1 - 20 / 20

[ Back to top ]