Fターム[5F036BB18]の内容

半導体又は固体装置の冷却等 (3,151) | 冷却装置 (1,063) | 放熱部材(ヒートシンクを含む) (507) | 電極 (2)

Fターム[5F036BB18]に分類される特許

1 - 2 / 2

半導体装置

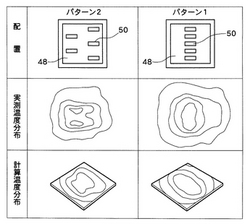

【課題】大電力用の半導体素子において、温度上昇分布をより均一にすることである。

【解決手段】電流が大きいために、上部電極層48の抵抗の場所的分布の影響を受け、上部電極層48内における複数の接続部50の平面配置条件に依存して半導体素子の温度上昇分布が定まる大電流用の半導体素子において、パターン2のようにジグザク状に接続部50を配置するのと、パターン1のように1列に接続部50を配置するとのでは、温度上昇分布が明らかに異なる。このことはシミュレーションの結果と定性的によい一致を示す。この他に、各ワイヤのそれぞれが、上部電極層48との間で複数の接続部を形成するようにしてもよい。

(もっと読む)

半導体装置、半導体モジュール及び半導体装置の製造方法

【課題】半導体モジュールに搭載する前のベアチップを保護して取り扱いやすくする。

【解決手段】ベアチップとして、Si半導体よりも高効率であり高温動作が可能であるSiC等の横型構造のワイドバンドギャップ半導体11を使用し、このワイドバンドギャップ半導体11の全ての電極を同一の主面に形成する。ワイドバンドギャップ半導体11の周囲を、AlN等のセラミック製の保護部材17でパッケージングし、ワイドバンドギャップ半導体11の電極が形成された主面を、AlN等のセラミック製の支持部材13で支持して、ワイドバンドギャップ半導体11の熱拡散効果を高め、且つ各部材同士の間の熱応力を緩和する。

(もっと読む)

1 - 2 / 2

[ Back to top ]