Fターム[5F064CC07]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | JFET (4)

Fターム[5F064CC07]に分類される特許

1 - 4 / 4

電界効果トランジスタ

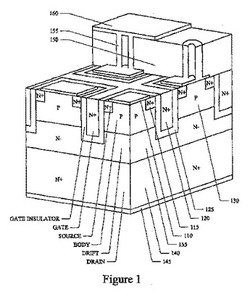

実施の形態に係る自己修復型電界効果トランジスタ(FET)装置は、各々がヒューズリンクを有する複数のFETセルを含む。ヒューズリンクは、対応するセルにおける高電流イベント時に飛ぶように調節される。 (もっと読む)

実質的に均一なパターン密度で形成された回路を有する半導体デバイス

半導体デバイスは、導電層から形成された少なくとも3つの導電配線(202、204、206)に結合された少なくとも1つのトランジスタ(T1)を有する第1の回路部分(200A)を含む。3つの導電配線のうちの1つ(204)は前記少なくとも1つのトランジスタの制御端子を形成する。また、第2の回路部分(200B)は、少なくとも2つのトランジスタ(T3−T6)を含む。該少なくとも2つのトランジスタの各々は、同一の導電層から形成された導電配線(234、236、238、240)によって形成された制御端子を有する。第1の回路部分の前記3つの導電配線は、第2の回路部分の導電配線群と同一のピッチパターンを有する。  (もっと読む)

(もっと読む)

金属層に接触しない接点ヒューズ

半導体デバイス・ヒューズ(100)は、金属層(105)および金属層をヒューズ層(115)に電気的に結合する第1の半導体層(110)を含む。ヒューズ層は、金属層から間隔を置いて配置されている。この半導体デバイス・ヒューズは、さらにヒューズ層とともにブロー接合インターフェイス(125)を形成する第2の半導体層(120)を含む。ブロー接合インターフェイスは、第2の半導体層を通じてヒューズ層に所定の電力が伝送されるときに、開放回路を形成するように構成されている。  (もっと読む)

(もっと読む)

電界効果トランジスタモデル、回路シミュレーション装置、回路シミュレーション方法、回路シミュレーション用プログラム及び記録媒体

【課題】 電界効果トランジスタの特性の正確なシミュレーションを可能とする電界効果トランジスタモデル、回路シミュレーション装置、回路シミュレーション方法、回路シミュレーション用プログラム及び記録媒体を提供する。

【解決手段】 電界効果トランジスタのAC特性及び雑音特性のシミュレーションを行うための電界効果トランジスタモデルにおいて、熱雑音を発生する第一抵抗と熱雑音を発生しない第二抵抗とを直列に接続した抵抗回路を電界効果トランジスタのゲート抵抗として接続する。

(もっと読む)

1 - 4 / 4

[ Back to top ]