Fターム[5F083ZA24]の内容

Fターム[5F083ZA24]に分類される特許

1 - 5 / 5

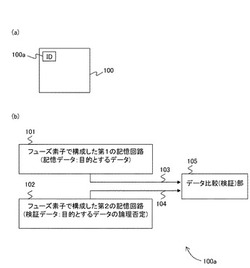

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

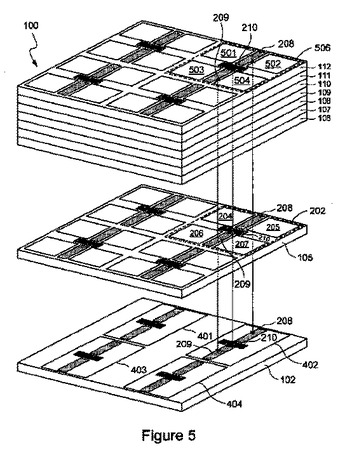

3次元メモリモジュールアーキテクチャ

本発明の様々な実施形態は、スタックされたメモリモジュールに向けられている。本発明の一実施形態において、メモリモジュール(100,600,1200,1400)は、少なくとも1つのメモリ層がスタックされた少なくとも1つのメモリコントローラ層(102,602,1204,1402)を備える。ファインピッチのスルー複数バイア(例えば、スルーシリコン複数バイア)(114,116)が、前記少なくとも1つのメモリコントローラ(401〜404)と、前記少なくとも1つのメモリ層との間の電気的な伝達を提供する前記スタックを通じて、前記少なくとも1つのメモリコントローラの表面に対してほぼ垂直に延在する。追加的には、前記メモリコントローラ層は、前記メモリモジュールに対して双方向にデータを伝達するよう構成された少なくとも1つの外部インターフェースを含む。更にまた、前記メモリモジュールには、光学層(602,1202)を含めることができる。該光学層を、前記スタック内に含めることができ、及び、該光学層は、前記少なくとも1つのメモリコントローラに対して双方向にデータを伝達するバス導波路を有する。前記外部インターフェースは、前記光学層とインターフェースする光学的な外部インターフェースとすることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 EPROMを搭載するICチップにおいて、データを消去するメモリ素子(書換え可能な)とデータを消去したくないメモリ素子(データ冗長用)を同時に有する半導体装置を提供する。

【解決手段】 特定のメモリ素子の上に紫外光線を反射、吸収する遮光物を形成する。このことによりデータ消去性を調整できるようなメモリ素子を形成できるようにする。また、遮光物に開口することで、より消去制御性のよりメモリ素子とすることができる。

(もっと読む)

強誘電体メモリ装置のリサイクル方法および強誘電体メモリモジュール

【課題】簡便にヒステリシス特性を回復させることのできる強誘電体メモリ装置のリサイクル方法および強誘電体メモリモジュールを提供する。

【解決手段】強誘電体メモリモジュール100を含む強誘電体メモリ装置のリサイクル方法であって、強誘電体メモリ装置から強誘電体メモリモジュールを取り外す工程と、前記強誘電体メモリモジュールを加熱する加熱工程と、を含む。

(もっと読む)

半導体装置

【課題】生産性が良く、安価な半導体装置を提供すること。

【解決手段】本発明の半導体装置において、半導体記憶素子5がガラス基板1に取り付けられると共に、半導体記憶素子5の電極7がガラス基板1に設けられた配線パターン2に接続されるため、従来に比して部品点数が少なくなって、生産性が良く、安価なものが得られる。

(もっと読む)

1 - 5 / 5

[ Back to top ]