Fターム[5F101BA68]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | その他記憶作用 (122) | 磁性体 (5)

Fターム[5F101BA68]に分類される特許

1 - 5 / 5

半導体装置

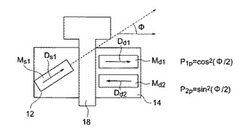

【課題】通常のC−MOSFET回路との整合性、混載可能性を保ちつつ安定した動作で、不揮発な再構成可能論理回路を構築することが可能なスピンMOSFETを備えた半導体装置を提供することを可能にする。

【解決手段】半導体基板と、半導体基板に離間して形成された第1ソース領域12および第1ドレイン領域14と、第1ソース領域と第1ドレイン領域との間に設けられる第1チャネル領域と、第1チャネル領域上に形成された第1ゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極18と、第1ソース領域上に形成され第1方向に磁化容易軸を有する強磁性層を含む第1ソース電極Ms1と、第1ドレイン領域上に形成され第1方向に対して0度より大きく180度未満の角度をなす第2方向に磁化した強磁性層を含む第1ドレイン電極Md1と、第1ドレイン領域上に第1ドレイン電極と離間して形成され第2方向と略反平行な方向に磁化した強磁性層を含む第2ドレイン電極Md2と、を備えている。

(もっと読む)

半導体集積回路

【課題】 信頼性高く不揮発記憶を書き込めるようにする。非記憶と不揮発記憶の両方、一時記憶(揮発記憶)と不揮発記憶の両方を一つの回路で行い得るようにする。

【解決手段】 前段回路の情報を状態検地強調回路Aを介して本段回路に書き込む。制御信号V selectがL、即ち/V selectがHの時、回路Aでは小電圧のVcc0とVss0が選択され、これが前段回路に印加される。この時、本段回路のn-Tr2のゲート-p型基板端子間には0V以上Vcc0-Vss0以下の電位しか印加されないのでオフとオンの判別が可能な程度にチャネル抵抗は変化するが十分な不揮発記憶書き込みを行うほどではない。V selectがH、即ち/V selectがLに変わると、回路Aでは大電圧のVcc3とVss3が選択され、これが前段回路に印加される。V selectがHになる直前のVnの論理がHならば、n-Tr2には不揮発オン状態の書込が行われ、p-Tr2には不揮発オフ状態の書込が行われる。

(もっと読む)

半導体メモリ

【課題】 情報の保持時間を確保できる半導体メモリを提供する。

【解決手段】 半導体メモリは、第1面を有する半導体基板1を有する。第1絶縁膜4aは、第1面上に設けられ、第1面と離れた位置に第1面内の第1方向に広がりを持つ溝11を有する。第2絶縁膜4bは、溝の開口を塞ぐように第1絶縁膜上に形成される。複数の微粒子12が、溝内に設けられる。ゲート電極G1は、溝の上方において第2絶縁膜上に設けられる。チャネル領域は、溝の下方の半導体基板の表面に設けられ、溝の第1方向における長さより短い第1方向における長さを有する。1対のソース/ドレイン領域S/Dが、チャネル領域を挟むように半導体基板の表面に設けられる。

(もっと読む)

電界効果トランジスタ及びその動作方法

【課題】 ゲート容量可変の電界効果トランジスタを用いた不揮発性メモリの消費電力と読み出しエラーとを低減する。

【解決手段】 シリコン基板101上にソース領域104とドレイン領域105を形成すると共にソース領域104とドレイン領域105とに挟まれた領域上に順次、絶縁膜102a、PCMO膜102b、ゲート電極103を積層して、電界効果トランジスタ1とする。PCMO膜102bに印加する書き込み電圧の電圧値を変えることによってデータを書き込み、PCMO膜102bに読み出し電圧を印加し、ドレイン電流を検出することによってデータを読み出す。

(もっと読む)

不揮発性メモリ回路

【課題】電源電圧を印加しなくてもデータを記憶できる不揮発性メモリ回路及び不揮発性メモリ装置に関し、書き込み・読み出しを最適に行なえる不揮発性メモリ回路及び不揮発性メモリ装置を提供することを目的とする。

【解決手段】本発明は、不揮発性メモリ回路であって、第1又は第2のビット線に印加される電圧により不可逆的に内部回路を劣化させてデータを不揮発的にラッチするフリップフロップと、フリップフロップの第1の出力端子と前記第1のビット線との間に接続された第1スイッチと、フリップフロップの第1の出力端子と第1のビット線との間に接続された第2スイッチと、フリップフロップの第1の出力端子の出力を反転した出力を行なう第2の出力端子と第2のビット線との間に接続された第3スイッチと、フリップフロップの第2の出力端子と第2のビット線との間に接続された第4スイッチとを有することを特徴とする。

(もっと読む)

1 - 5 / 5

[ Back to top ]