Fターム[5F101BD44]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 表面保護膜 (105) | PSG (4)

Fターム[5F101BD44]に分類される特許

1 - 4 / 4

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】スプリットゲート型の不揮発性半導体記憶装置において、読み出し速度と消去速度を向上させること。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1中のチャネル領域上のゲート絶縁膜上に並んで形成されたコントロールゲート22及びフローティングゲート3と、フローティングゲート3の上面FUSと対向し全体がその上面FUSよりも上に位置する消去ゲート10と、を備える。フローティングゲート3の上面FUSは、対向する第1辺FE1と第2辺FE2を含む。消去ゲート10の底面EBSは、第1辺FE1と第2辺FE2との間の上面FUSよりも第1辺FE1及び第2辺FE2に近い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】スプリットゲート型の不揮発性半導体記憶装置において、消去ゲートと対向するフローティングゲートの鋭角部をより尖らせること。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1中のチャネル領域上のゲート絶縁膜上に並んで形成されたコントロールゲート22及びフローティングゲート3と、フローティングゲート3の上面FUSと対向する消去ゲート10と、を備える。フローティングゲート3の側面は、対向する第1側面FSS1と第2側面FSS2を含む。第1側面FSS1と第2側面FSS2の間隔は、上面FUSから半導体基板1側に向かうにつれて狭くなる。

(もっと読む)

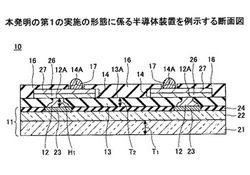

半導体装置及びその製造方法

【課題】特性バラツキを低減し、動作信頼性を向上出来る半導体装置及びその製造方法を提供すること。

【解決手段】 メモリセルMTと、第2素子分離領域によって互いに電気的に分離された第2半導体領域上に形成された抵抗素子と、前記第2素子分離領域直下に形成された第3半導体領域47とを具備し、抵抗素子は、前記第2半導体領域10上に第3絶縁膜60を介在して形成された導電体層12と、前記導電体層12の両端に電気的に接続された第1電極14、15及び第2電極14、15と、前記第1、第2電極14、15を電気的に分離する電極分離領域44とを備え、前記電極分離領域44に隣接する前記第2素子分離領域は表面に凹部38を有し、前記第3半導体領域47は、前記第1導電型と逆導電型の第2導電型を有し、前記第2素子分離領域の前記凹部38直下に設けられている。

(もっと読む)

1 - 4 / 4

[ Back to top ]