Fターム[5F102GC01]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 横型FETの上部ゲート (2,283)

Fターム[5F102GC01]に分類される特許

2,281 - 2,283 / 2,283

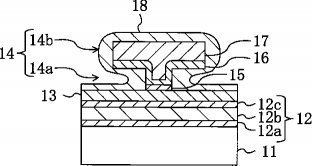

マイクロストリップ線路、その製造方法、インダクタ素子及び高周波半導体装置

【課題】 マイクロストリップ線路の線路幅の狭小化を行なったとしても、導体損失が増加しないようにする。

【解決手段】 半絶縁性GaAsからなる基板11上には、接地電極12と、厚さが約0.5μmのチタン酸ストロンチウムからなる誘電体層13と、線状導体層14とにより構成されるマイクロストリップ線路が形成されている。線状導体層14は、幅が約0.5μmの狭小部14aと、幅が約5μmの幅広部14bとにより構成されている。この線状導体層14は、異なる材料からなる積層体であって、基板11側から順次形成された、厚さが約0.1μmの窒化タングステンシリコンからなる第1層15と、厚さが約0.05μmのTiと厚さが約0.5μmのAuとの積層体からなる第2層16と、厚さが約3μmのAuからなる第3層17とから構成されている。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】耐圧性、特性安定性に優れ、ゲートリーク電流が低減されたヘテロ接合型電界効果トランジスタを提供すること。

【解決手段】半導体基板上にバッファ層と、チャネル層と、スペーサ層と、キャリア供給層と、ショットキーバリア層と、高濃度不純物ドープキャップ層とが順次堆積され、ソース電極及びドレイン電極がキャップ層表面に形成され、ソース電極とドレイン電極の間のキャップ層にショットキーバリア層に達する開口部が形成され、開口部に露出したショットキーバリア層表面にゲート電極が形成されているヘテロ接合型電界効果トランジスタであって、キャップ層が複数の細線で構成され、細線間はショットキーバリア層が露出し、ソース電極及びドレイン電極が、細線と細線間に露出したショットキーバリア層との両方に接触していることを特徴とするヘテロ接合型電界効果トランジスタを構成する。

(もっと読む)

伝送線路、その電気的特性の調整方法、およびマイクロ波モノリシックIC

【課題】 コンパクトかつ電気的特性の良好な高性能・高歩留まりの高周波伝送線路およびその電気的特性の調整方法の提供を目的とする。

【解決手段】 コプラナ・ウェーブガイドのグラウンドパターン5の一部の上部に薄膜誘電体層6を選択的にパターニングして配置し、この薄膜誘電体層6の上に島状メタルパターン7を一定間隔で複数個配置する。島状メタルパターン7相互間、信号線4と島状メタルパターン7間、および島状メタルパターン7とグラウンドパターン5間の必要部分について、ボンディングワイヤ8で接続する。

(もっと読む)

2,281 - 2,283 / 2,283

[ Back to top ]