Fターム[5F102HB05]の内容

接合型電界効果トランジスタ (42,929) | セルフアライン、複数の素子部分の形成 (18) | 形成する部分 (14) | リセス (5)

Fターム[5F102HB05]に分類される特許

1 - 5 / 5

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

リセスゲート型HFETの製造方法

【課題】安定してノーマリオフ特性を有するリセスゲート型HFETを製造することができるリセスゲート型HFETの製造方法を提供する。

【解決手段】基板上にGaN層とAlGaN層とのヘテロ接合部を有し、AlGaN層上にゲート電極が形成されているリセスゲート型HFETを製造する方法であって、基板上にGaN層を形成する第1工程と、GaN層上に第1のAlGaN層を1nm以上3nm以下の厚さに形成する第2工程と、第1のAlGaN層の表面のうちゲート電極形成領域以外の領域の少なくとも一部の表面上に第2のAlGaN層を再成長により形成する第3工程と、第1のAlGaN層の表面のゲート電極形成領域にゲート電極を形成する第4工程と、を含む、リセスゲート型HFETの製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】 ゲートリセス構造を有する高周波素子等の半導体装置を良好な歩留まりで製造することのできる半導体装置の製造方法を得る。

【解決手段】 第2の絶縁膜4を堆積する膜厚を所定のあらかじめ厚さとし、この第2の絶縁膜をエッチングする時間を所定の時間とすることによって、開口3の周縁に形成されるサイドウォール5の断面幅を調整し、後の工程にてこのリセス7が形成される半導体基板1の露出部位6の幅を所望の値に制御する。また、この半導体基板1の露出部位6にリセスを形成する際は、そのエッチング時間を制御することによって形成されるリセス7の深さを所望の値に制御する。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有し、歩留が改善する半導体装置の製造方法を提供すること。

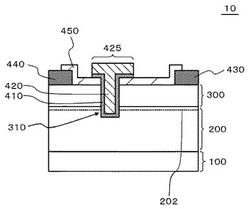

【解決手段】電子供給層13およびキャップ層14を設けた半導体基板10上に第1絶縁膜15を堆積する第1工程と、半導体基板10上にレジスト膜16を形成する第2工程と、レジスト膜16に開口16aを形成する第3工程と、開口16aを通して第1絶縁膜15をエッチングし開口15aを形成する第4工程と、レジスト膜16を剥離する第5工程と、第1絶縁膜15の開口15aを通して、電子供給層13と選択的にキャップ層14をエッチングし開口14aを形成する第6工程と、キャップ層14の開口14aを塞がない膜厚の第2絶縁膜17を堆積する第7工程と、第2絶縁膜17にエッチバック処理を行い電子供給層13を露出させる第8工程と、第2絶縁膜17をマスクにして電子供給層13を所定の深さまでエッチングする第9工程と、電子供給層13上にゲートメタル20を形成する第10工程とからなる。

(もっと読む)

1 - 5 / 5

[ Back to top ]