Fターム[5J042BA06]の内容

論理回路 (4,317) | 論理回路の種類 (1,203) | 構成要素がマトリックス状に配置されたもの (595) | PLA (556) | 積項線又は和項線を分割するもの (5)

Fターム[5J042BA06]に分類される特許

1 - 5 / 5

可変遅延回路およびその制御方法

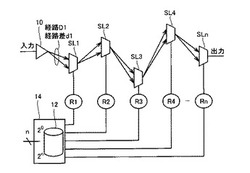

【課題】信号の遅延量を微調整可能な可変遅延回路を提供する。

【解決手段】可変遅延回路において、N個の可変論理回路を用いてN段のセレクタが直列接続される。1段目のセレクタSL1の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D1には経路差d1が存在している。また、2段目のセレクタSL2の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D2には、経路差d2が存在している。信号が通過する当該経路の組み合わせは、セレクタSLの段数に基づき、N段であるため2nとおりの信号経路の組み合わせが生じる。すなわち、2nとおりの切替信号R1〜Rnの組み合わせに基づいて2nとおりの信号経路が選択される。2nとおりの信号経路の組み合わせに基づく配線経路差に基づいて信号遅延量を調節する。

(もっと読む)

再設定可能な論理回路のための電子機器

本発明は、互いに電気的に接続された電界効果トランジスタおよび抵抗スイッチを含む電子機器に関する。前記電子機器において、前記抵抗スイッチは、低抵抗の状態と高抵抗の状態との間で切り替えられるように構成される。 (もっと読む)

互い違いにされた論理アレイブロックのアーキテクチャ

【課題】各論理アレイブロック(LAB)が、単一の伝導体チャンネルだけを使用して、または伝導体チャンネルを全く使用することなく、より多くの数の他のLABと通信することを可能にするアーキテクチャを提供すること。

【解決手段】集積回路(IC)デバイスであって、実質的に互いに整列された第1のグループの論理アレイブロックと、実質的に互いに整列され、かつ、複数の水平方向の伝導体および垂直方向の伝導体によって該第1のグループのLABに結合された第2のグループのLABとを備えており、該第1のグループおよび該第2のグループにおける各LABは、同じ数の論理要素(LE)を備えており、該第1のグループのLABは、実質的に、各LAB内のLEの数の半分だけ該第2のグループのLABからオフセットされている、集積回路(IC)デバイス。

(もっと読む)

半導体集積回路

【課題】基本構成単位となる回路セルの無駄を減らし、回路サイズの増大を抑えることができる半導体集積回路を提供する。

【解決手段】選択部10において4つの選択入力信号(SIN1〜SIN4)の中から1つ又は複数の信号が選択され、セル出力信号として回路セル外部に出力される。制御信号生成部20では、セル入力信号A,Bに応じて、選択部10の選択動作を制御するための制御信号が生成される。そしてプログラム部30では、選択部10の複数の選択入力信号(SIN1〜SIN4)それぞれに対し、論理値「0」の信号、論理値「1」の信号、セル入力信号(C,/C,D,E,F)の何れか1つが、回路セルの論理機能に応じて割り当てられる。

(もっと読む)

マルチプライヤを含んだプログラマブルロジックデバイスならびにそのリソース使用を低減するための構成

【課題】リソースの使用を低減するよう構成されるマルチプライヤ回路を備えたプログラマブルロジックデバイスの提供。

【解決手段】専用のマルチプライヤ回路を有するプログラマブルロジックデバイスにおいて、通常はデバイスの検査に使用されるスキャンチェーンレジスタのいくつかがマルチプライヤの入力に近接して配置される。スキャンチェーンレジスタは入力レジスタとAND演算され、1および0のテンプレートでロードできる。これにより、例えば最も重要でないビットに0がロードされ残りのビットに1がロードされた場合にサブセット乗算が可能になる。マルチプライヤは他の構成要素と共にブロック構成され、有限インパルス応答(FIR)フィルタとして構成可能になる。この構成においてフィルタ係数をロードするためスキャンチェーンレジスタを使用し得、デバイス上の限られたロジックおよびルーティングリソースの使用を回避する。

(もっと読む)

1 - 5 / 5

[ Back to top ]