Fターム[5J056AA38]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 信号幅の変換 (3)

Fターム[5J056AA38]に分類される特許

1 - 3 / 3

レベルシフタおよび高電圧論理回路

入力および出力信号の電圧振幅に対して低い絶縁破壊電圧を有するMOSトランジスタで実施されるレベルシフタと高電圧論理回路が、記載されている。例示的な設計では、レベルシフタ(102)はドライバ回路(110)とラッチ(140)とを備えている。ドライバ回路は、第1の電圧範囲を有する入力信号(Vinp、Vinn)を受信し、第2の電圧範囲を有する駆動信号(Vdrp、Vdrn)を与える。第1および第2の電圧範囲は、正および負の電圧、または正の電圧の異なる範囲を含むことができる。ラッチは、駆動信号を受信し、第2の電圧範囲を有する出力信号(Voutp、Voutn)を与える。ドライバ回路は、入力信号に基づいて全電圧範囲を有する制御信号(Vctrip、Vctrin)を発生することができ、その後、制御信号に基づいて駆動信号を発生することができる。レベルシフタを使用して、高電圧論理回路を実施することができる。  (もっと読む)

(もっと読む)

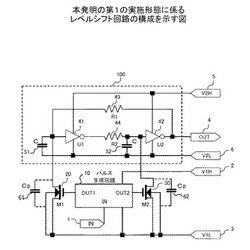

レベルシフト回路およびこれを用いたDC−DCコンバータ

【課題】低電位系のMOSFETのドレイン−基板間に存在する寄生容量の影響により高電位系のラッチ回路が誤動作してしまうことを防止するレベルシフト回路を提供する。

【解決手段】本実施形態では、容量(C)51,52を配することにより、ノイズを吸収してラッチ回路100の誤動作を防止している。即ち、ラッチ回路100のインバータ(U1)41,インバータ(U2)42の入力端子と、高電位系であるラッチ回路100の基準電圧となる端子(V2L)6との間に、容量(C) 51,52を接続しているので、ノイズを容量(C)51,52に吸収させることが可能となり、ラッチ回路100の誤動作を防止することができる。

(もっと読む)

レベル設定回路

【課題】 信号を所定のレベルに設定して出力させることができ、かつ、プロセスばらつきによる設定レベルのばらつきを小さくすることができるレベル設定回路を提供する。

【解決手段】 ベースを入力、エミッタを出力とするバイポーラトランジスタQ2を用いたエミッタフォロワにかかる。バイポーラトランジスタQ2のベースとエミッタとを第1の負荷抵抗2が接続している。バイポーラトランジスタQ2のコレクタ側へとつながる所定電位とベースとを第2の負荷抵抗3が接続している。バイポーラトランジスタQ2のベースに直列にスイッチSW1が接続されている。

(もっと読む)

1 - 3 / 3

[ Back to top ]